#### This manual has been reproduced from a 1972 Russian publication written by

#### А. Г. БОБРОВ, and И. И. БИГЛЕР

#### Entitled

# Design, Maintenance, Service and Operation EKVM "Soemtron-220"

We (<u>www.soemtron.org</u>) fully recognise the intellectual property rights of the originating source and will take steps to remove, alter or further acknowledge this document if we are notified of any infringements. It has been presented in good faith to aid in understanding the inner workings of the now vintage Soemtron 22x range of electronic calculators.

It has been published by us to disseminate information about the Soemtron 22x range of electronic desk calculators manufactured by V.E.B. (\*1) Büromaschinenwerk Sömmerda, as a project to gather and centralise whatever information can be found about these increasingly rare early electronic calculators.

If you have or know of any information, books, drawings, circuits, hardware, test equipment (prufgerat) or other memorabilia relating to the Soemtron 220, 221, 222 or 224 calculators, their trade names - Daro or Soemtron, manufactured by - V.E.B. Büromaschinenwerk Sömmerda, please email us at - <u>mike@soemtron.org</u>

This document has been scanned from an original book, processed through a commercial Cyrillic OCR software package to regenerate the original Russian text and then automatically translated to English and imported into Microsoft Word. Layout has been duplicated in line with the original document as much as possible to retain the flow of the original document. Drawings, circuits and photographs are scans from the original document.

With this effort in mind some of the syntax presented here is a little strange to say the least!. Some portions have been reworked to be more readable English text but there is obviously more to be done. If you can help with this, or indeed have any helpful information or comments, please email us at - <u>mike@soemtron.org</u>

Please use, and hopefully enjoy, this in information in the spirit in which we undertook to generate it - as an information source for an interesting piece of early calculator history before the advent of modern electronics, in the days when "hands on" engineers thought through the problems and challenges of designing equipment with little resources, to produce the best end product they could.

June 2009 www.soemtron.org mike@soemtron.org

# TSCSU OF THE USSR ALL-UNION STATE

The Design Institute of Technology for the Mechanization of Calculation and Computational works.

Central Administrative Board of Preparation and Improvements of Professional Workers Skills.

# А. Г. БОБРОВ, И. И. БИГЛЕР

Design, Maintenance Service and Operation EKVM "Soemtron-220"

The questions of administrative decision of work is at present now inseparably connected with the application of contemporary computer technology, with one of the most of labour-consuming divisions appears the processing economic information. In recent years fast manufacturing growth and the introduction of a large quantity of electronic key-actuated computers for processing of economic information is seen. The effective application of new high-productivity electronic key-actuated computers requires the imperative systematic preparation and increasing qualification standard of maintenance of personnel.

The manual is written in strict conformity with the course program of the study of « Soemtron-220 » machines in the training network of the main administration of preparation and increase in the qualification of the workers of the calculation of TscSu of the USSR (Central Statistical Office of the USSR). The primary goal of the present manual is to render assistance to the pupil, students of corresponding specialities, and also workers of computing stations and bureau in the application and studying of a design and service maintenance of the electronic keyboard computer « Soemtron-220 ».

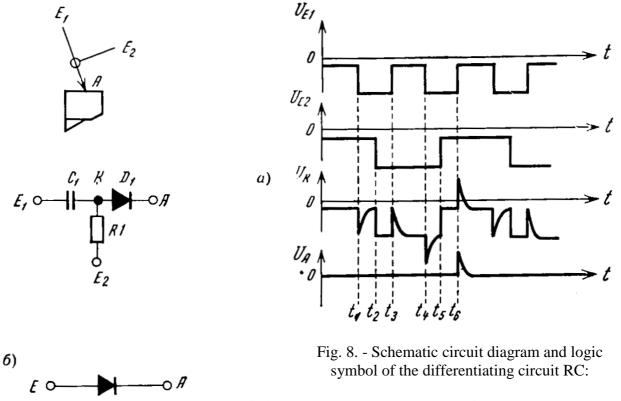

A characteristic property in the construction of the machine is the use of « AND » logic circuits, and the wide application of controlled differentiating circuits, I.E. differentiating circuits with the performance of logical functions.

# **Chapter I**

# DESIGN AND THE APPLICATION OF EKVM\* « SOEMTRON-220 »

# 1.1. TECHNICAL AND OPERATING CHARACTERISTICS

## **1.1.1.** Purpose and the general description.

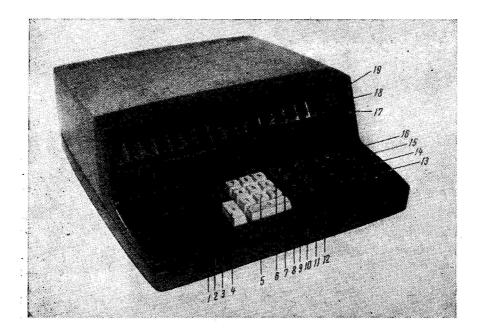

The electronic computer model « Soemtron-220 » (Fig. 1) can be related to the type of electronic key-actuated computers with manual entry of information with a sequential operating principle. Entry of digital information is provided by the decimal digital keyboard.

The arithmetic operations of Addition, Subtraction (striking a balance), Multiplication, Division and Exponentiation are carried out taking into account the sign of the number. The arithmetic operations of multiplication and division are carried out with the set degree of accuracy and with a rounding off of the last digit.

The memory unit consists of three operational and three accumulator registers each with a capacity of 15 digits.

Display of entered information and the results of calculations are provided by 15 digital lamps. The sign of the number is shown by the  $\ll - \gg$  sign indicator.

The presence of the accumulator registers ensures appropriate effectiveness during the solution of different kinds of tasks, I.e. it creates an opportunity for entry and use of constants, and allows the accumulation and storage of the necessary intermediate and final results of calculations. Except for performance of arithmetic operations, the machine automatically provides control of exceeding register length.

Addition and Subtraction operations occur in 5ms, multiplication and division - on average take 0.5 seconds, with a clock pulse generator frequency of 25KHz. Presence of an automatic rounding off of the last entry in multiplication and division testifies to convenience and expediency of the machine for processing in economic information applications. This machine can also be successfully used for different technical-engineering calculations.

The unit type principle of the assembly of separate units is assumed as the basis of construction of the machine. Essentially the computer is an arithmetic-logic unit, whose design is made on the basis of diode-transistor elements in combination with a magnetic storage array composed of ferrite cores, assembled into digital matrices.

Fig. 1. The common form of electronic key-actuated computer "Soemtron-220":

1 - Rotary decimal point selection switch; 2 – Lö clears the machine and erases information in the operational registers; 3 - Clear entry key for the most recently input information; 4 - Decimal point key; 5 - Digital keyboard; 6 - Negate entry key; 7 - Multiplication; 8 - Addition, 9 - Involution; 10 - Division; 11 - Subtraction; 12 - Result key; 13 - Add to accumulator registers 1-3; 14 - Subtract from accumulator registers 1-3; 15 - Return the intermediate sum of accumulator registers 1-3; 16 - Return final sum of accumulator registers 1-3; 17 - Digital display; 18 - « — » sign indicator; 19 <sup>-</sup> Mains on indicator.

The memory unit consists of six independent memory registers MD, MR, AC0, AC1, AC2 and AC3, each of which is capable of storing 15 decimal digits of information plus the sign of the number.

According to its designation the registers can be divided into the operational (MD, MR and AC0) and accumulating (AC1, AC2 and AC3).

The operational registers serve to store the entered digital information, sign of the number and intermediate and final results of the arithmetic operation performed.

The accumulator registers are used for storing of digital information, also the sign of the number, intermediate and final results of calculations.

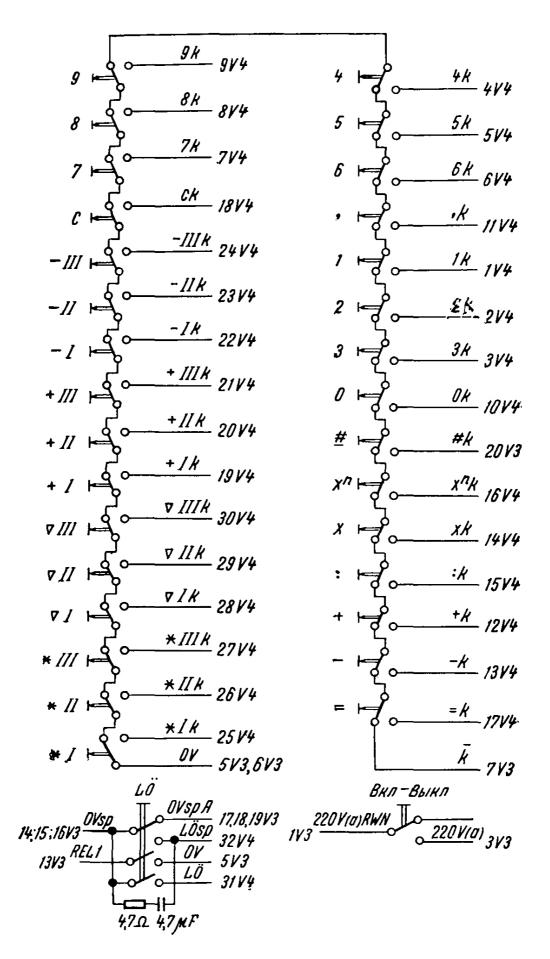

Digital information, sign of the number, and the arithmetic operation are entered into the arithmetic-logic unit during closing and switching of the corresponding contacts of the digital and functional keys on the keyboard.

The entered digital information, results of arithmetic operations, intermediate and final results of calculations are displayed on the display unit using luminous digital lamps. The display unit has a maximum capacity of 15 decimal digits plus sign.

The integer part of the number is separated from the fractional by setting the decimal point position switch to the desired degree of calculation accuracy. The selected decimal point position is shown by an illuminated incandescent lamp in the appropriate position of the display.

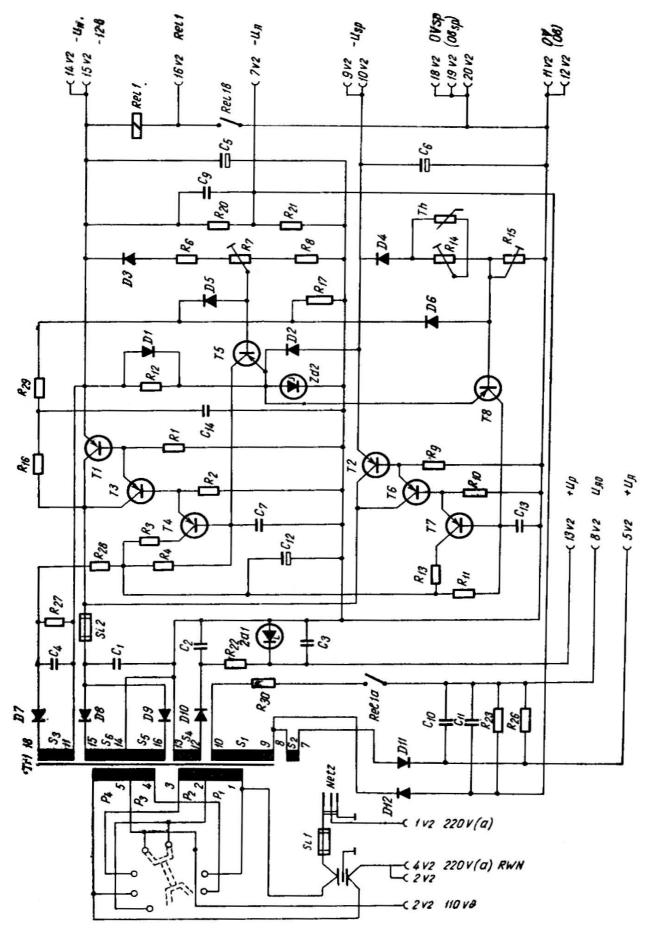

The integral power unit provides all the necessary operational stabilized and non-stabilized supplies.

The supply line voltage with a frequency of 50Hz must be within the limits 220Vac  $^{+10\%}_{-15\%}$ , -110Vac  $^{+10\%}_{-15\%}$ , at a consumed power of 50 W. Overall size of the machine is: width - 380mm, length - 464mm, height - 194mm, weight - is 15 kg.

# **1.1.2.** Preparation of the machine for operation.

The computer is delivered from the manufacturer set for a mains supply of alternating current with a voltage of 220V at  $^{+10\%}_{-15\%}$ , with a frequency of 50 Hz.

Before connecting the machine to the mains supply it is necessary to remove upper rear cover and to check that the voltage selector switch of the power unit corresponds to the line voltage of your mains supply.

The setting of the voltage selector switch on power unit makes it possible to adjust the connection of the machine to the AC mains network for voltages of 220V or 127V. After setting the voltage selector switch to the correct line voltage, the removed cover must be replaced.

The assembled machine with mains supply lead should be connected to the mains supply with a master switch. Rotating the « ON-OFF » switch connects the line voltage to the primary winding of transformer and illuminates the « mains on » pilot lamp on the display unit (Fig. 1).

Pressing the « Lö » key ensures the erasure of the information in the operational registers MD, MR, AC0 and resets the network elements to an initial state, enables the power unit and clears the display. On enabling the power unit, the correct voltages which ensure the operation of the arithmetic-logic and display units, are output. As a result of the controlled erasure of the operational registers this ensures all digital lamps of the display unit show the number zero.

Pressing the keys « \*I », « \*II », « \*III » in sequence ensures the erasure of the accumulator registers AC1, AC2, AC3, I.E. the re-writing of digital information from the accumulator registers AC1, AC2, AC3 into the operational register MR (rewritten digital information in the accumulator registers is not retained) the previously written digital information into register MR is erased during the re-writing from the sequential accumulator register. After recall of the last accumulating register digital information in the MR register is erased by pressing the « C » key.

As a result of this serial operation of the enumerated functional keys the arithmetic-logic unit of the machine is completely prepared for completing arithmetic operations.

Rotating the decimal point selection switch sets the correct level of accuracy for calculations.

# **1.2.** Performance of arithmetic operations.

Entry of the digital information is made through the digital decimal keyboard by a consecutive set of figures, beginning from the high-order digit of the number (Fig. 1). Entry of mixed digital information occurs with inclusion of the «, » key after the whole part of a number. When the entered number has no fractional part and also when the fractional part has smaller quantity of decimal figures, than is established by the decimal point switch, entry of extra zeros is not required.

The position of the decimal point switch provides automatic completion of the length of entered numbers, I.E. the automatic addition of a corresponding quantity zeros after the inclusion of a necessary functional key. After setting the decimal point switch, the position of the decimal point is shown by an illuminated miniature incandescent lamp between the corresponding digital lamps of the digital display to create the illusion of a «, ».

# 1.2.1. Addition.

Addition operations are performed by the arithmetic-logic unit with the result of the sum in the operative register AC0 or in the accumulating registers AC1, AC2 or AC3.

For performance of operations in a certain sequence the following function keys are used: « + », « = », « +I », « +II », « ▼II », « ▼II », « ▼II », « \*II », « \*III ».

Example 1. a + b = c 197 + 454 = 651.

| Order of operation                 | Function key | Display                                 |

|------------------------------------|--------------|-----------------------------------------|

| 1. Erase the operational registers | « Lö »       | 000000000000000000000000000000000000000 |

| 2. Decimal point switch setting    | « 0 »        | 0000000000000000                        |

| 3. Enter the first term 197        | « + »        | 000000000000197                         |

| 4. Enter second term 454           | « + »        | 00000000000454                          |

| 5. Result                          | « = »        | 000000000000651                         |

Example 2. a + b = c 265,12 + 165,437 = 430,557.

| Order of operation                 | Function key | Display          |

|------------------------------------|--------------|------------------|

| 1. Erase the operational registers | « Lö »       | 0000000000000000 |

| 2. Decimal point switch setting    | « 3 »        | 0000000000000000 |

| 3. Enter the first term 265,12     | « + »        | 00000000265,120  |

| 4. Enter second term 165,437       | « + »        | 00000000165,437  |

| 5. Result                          | « = »        | 000000000430,557 |

The position of the decimal point switch is determined by the required degree of accuracy or by the term with the greatest quantity of the numbers after the decimal point.

Addition with a different number of terms is carried out in a similar manner to the examples above. The small difference is to press the Addition  $\ll + \gg$  key after the entry of each term independent of the number of terms and continue in this way until a final result is obtained by pressing the  $\ll = \gg$  key.

To display an intermediate sum you should press the  $\ll = \gg$  key, after which continue with an Addition  $\ll + \gg$  key in the usual manner to continue the sequence. In the examples above the obtained sum was written into the operational register AC0. The result key ensures the storage of the digital information and sign of the number into register MR with the erasure of information in register AC0. The transfer of the sum into the accumulator registers is produced by pressing the appropriate

keys « +I », « +II », « +II », « +III », which ensure the storage of information from register MR into registers AC1, AC2 and AC3 without the erasure of information in the MR register.

The Addition operation with the use of the accumulator registers is examined below.

| Order of operation                  | Function keys           | Display                                 |

|-------------------------------------|-------------------------|-----------------------------------------|

| 1. Erase the accumulating registers | « *I » « *II » « *III » |                                         |

| 2. Erase the operational registers  | « Lö »                  | 000000000000000000000000000000000000000 |

| 3. Decimal point switch setting     | « 2 »                   | 0000000000000,00                        |

| 4. Enter the first term 342,35      | « +I »                  | 000000000342,35                         |

| 5. Enter second term 127,23         | « +I »                  | 000000000127,23                         |

| 6. Result                           | « I*»                   | 000000000469,58                         |

| Example 3. | a+b=c | 342,35 + 127,23 = 469,58 |

|------------|-------|--------------------------|

|------------|-------|--------------------------|

In this example the obtained sum was written into register AC1. With the serial use of the  $\ll +I \gg$ ,  $\ll +II \gg$ ,  $\ll +III \gg$  keys the sum of 469,58, besides register AC1, will also be written into registers AC2 and AC3. Pressing the  $\ll *1 \gg$  key ensures the recall of the contents from register AC1 into MR with the erasure of the contents in register AC1.

After completion of the Addition operation with storage of the sum in registers AC1, AC2 and AC3, pressing the corresponding key  $\langle + \nabla I \rangle$ ,  $\langle + \nabla II \rangle$ ,  $\langle + \nabla III \rangle$  ensures the display of the intermediate sum, I.E. recall without the erasure from registers AC1, AC2 and AC3 into register MR consequently, after pressing the keys for intermediate sums the information in the appropriate registers remains.

#### 1.2.2. Subtraction.

A Subtraction operation is carried out by the arithmetic unit with storage of a difference in he operative register AC0 or in accumulating registers AC1, AC2 and AC3.

The display of negative values of the entered digital information is ensured by illumination of the miniature incandescent lamp  $\ll - \gg$ .

For completion of an operation in the specific sequence these functional keys are used: «+», «-», «=», «+I», «+II», «+III», «-I », «-II », «-III», « ▼I », « ▼II», « ▼III», « \*I », « \*II », « \*III ».

| Exampl | e | 4. |

|--------|---|----|

|--------|---|----|

| Order of operation                | Function keys             | Display           |

|-----------------------------------|---------------------------|-------------------|

| 1. Erase the accumulating regist  | ters «*I » «*II » «*III » |                   |

| 2. Erase the operational register | s « Lö »                  | 000000000000000   |

| 3. Set decimal point switch       | « 3 »                     | 000000000000,00   |

| 4. Enter minuend 397,46           | « + »                     | 000000000397,460  |

| 5. Enter subtrahend 123,134       | «—»                       | 000000000123,134- |

| 6. Result                         | « = »                     | 000000000274,326  |

The position of the decimal point switch is the same as that used for Addition. Subtraction with a large quantity of subtrahends is carried out in a similar manner to the examples above. The small difference is to press the subtract key  $\ll - \gg$  after the entry of each subtrahend independent of their quantity and to continue in this way until a final result is obtained by pressing the  $\ll = \gg$  key.

In this example the difference obtained was written into the operational register AC0. Pressing the result key ensures the return of information from the AC0 register into the MR register with the erasure of the information in the AC0 register.

The transfer of difference into the accumulator registers is produced by pressing  $\ll +I \gg$ ,  $\ll +II \gg$ ,  $\ll +III \gg$  keys, which ensure the storage of information from register MR into the appropriate registers AC1, AC2, AC3 without the erasure of information in the MR register.

Below is an example of Subtraction using the accumulator registers.

#### Example 5. a - b = c 679,38 - 243,15 = 436,23

| Order of operation                  | Function keys           | Display          |

|-------------------------------------|-------------------------|------------------|

| 1. Erase the accumulating registers | « *I » « *II » « *III » |                  |

| 2. Erasure of operational registers | « Lö »                  | 0000000000000000 |

| 3. Set decimal point switch         | « 2 »                   | 0000000000000,00 |

| 4. Enter minuend 679,38             | « + »                   | 000000000679,38  |

| 5. Enter subtrahend 243,15          | « -I »                  | 000000000243,15- |

| 6. Result                           | « * »                   | 000000000436,23  |

In the given example the difference obtained was written into register AC1. With serial use of the « +I », « +II », « +III », « -I », « -II », « -III » keys, the Subtraction result 436,23, besides register AC1, will also be stored into registers AC2 and AC3,

Pressing the « \*I » key ensures the recall of difference from the AC1 register into the MR register with the erasure of register AC1. After completion of the subtraction operation with the storage of the difference in registers AC1, AC2 and AC3, pressing the «  $\forall I$  », «  $\forall II$  » and «  $\forall III$  » keys ensures the display of the intermediate difference, I.E. the recall of information without the erasure from the appropriate registers AC1, AC2 or AC3 into the MR register. Consequently, after pressing those keys the information in registers remains.

Example 6. a - b = -c when a < b235,24 - 467,496 = - 232,256 (striking a balance)

| Order of operation                 | Function key | Display          |

|------------------------------------|--------------|------------------|

| 1. Erase the operational registers | « Lö »       | 000000000000000  |

| 2. Decimal point switch setting    | « 3 »        | 000000000000,000 |

| 3. Enter of minuend 35,24          | « + »        | 00000000235,240  |

| 4. Enter of subtrahend 467,496     | «—»          | 00000000467,496- |

| 5. Result                          | « = »        | 00000000232,256- |

When as a result the completion of any operation gives a negative result, the miniature incandescent lamp is illuminated, to show a display of sign  $\ll - \gg$ .

# Example 7. (a) + (-b) = -c(+479,43) + (-735,64) = -256,21

| Order of operation                                           | Function key | Display          |

|--------------------------------------------------------------|--------------|------------------|

| 1. Erase the operational registers                           | « Lö »       | 000000000000000  |

| 2. Decimal point switch setting                              | « 2 »        | 0000000000000,00 |

| 3. Enter the first term 479, 43                              | « + »        | 000000000479,43  |

| 4. Enter second term 735,64<br>and press negation « -# » key | « + »        | 000000000735,64- |

| 5. Result                                                    | « = »        | 000000000256,21- |

# Example 8. (+a) - (-b) = c(+398,49) - (-635,78) = 1034,27

| Order of operation                                          | Function key | Display          |

|-------------------------------------------------------------|--------------|------------------|

| 1. Erase the operational registers                          | « Lö »       | 0000000000000000 |

| 2. Decimal point switch setting                             | « 2 »        | 0000000000000,00 |

| 3. Enter of minuend 398,49                                  | « + »        | 000000000398,49  |

| 4. Enter subtrahend 635,78<br>and press negation « -# » key | «—»          | 000000000635,78- |

| 5. Result                                                   | « = »        | 000000001034,27  |

Example 9. (a+b) - (c+d) + (k-l) = z(235,46 + 1357,28) - (174,27 + 459,96) + (547,54 - 2375,49) = -869,44

| Order of operation                                      | Function key               | Display           |

|---------------------------------------------------------|----------------------------|-------------------|

| 1. Erase accumulator registers                          | « *I », « *III », « *III » |                   |

| 2. Erase the operational registers                      | « Lö »                     | 00000000000000000 |

| 3. Decimal point switch setting                         | « 2 »                      | 000000000000,00   |

| 4. Enter the first term 235,46                          | « +I »                     | 000000000235,46   |

| 5. Enter second term 1357,28                            | « +I »                     | 000000001357,28   |

| 6. Result of the first sum                              | « ▼I »                     | 000000001592,74   |

| 7. Enter third term 174,27                              | « +II »                    | 000000000174,27   |

| 8. Enter fourth term 459,96                             | « +II »                    | 0000000000459,96  |

| 9. Result of the second sum                             | « ▼II »                    | 000000000634,23   |

| 10. Subtract second accumulator register from the first | « -I »                     | 000000000634,23   |

| 11. Result of first and second sums                     | « ▼I »                     | 000000000958,51   |

| 12. Enter minuend 547,54                                | « +III »                   | 000000000547,54   |

| 13. Enter subtrahend 2375,49                            | « -III »                   | 000000002375,49   |

| 14. Result of the third sum                             | « ▼III »                   | 000000001827,95   |

| Order of operation                     | Function key | Display          |

|----------------------------------------|--------------|------------------|

| 15. Add to third accumulating register | « +I »       | 000000001827,95- |

| 16. Final result                       | « *I »       | 000000000869,44- |

Shown below is example 9 using just one of the accumulating registers.

| Order of operation                                                        | Function key              | Display          |

|---------------------------------------------------------------------------|---------------------------|------------------|

| 1. Erase accumulator registers                                            | « *I », « *II », « *III » |                  |

| 2. Erase the operational registers                                        | « Lö »                    | 0000000000000000 |

| 3. Decimal point switch setting                                           | « 2 »                     | 0000000000000,00 |

| 4. Enter the first term 235,46                                            | « + »                     | 000000000235,46  |

| 5. Enter second term 1357,28                                              | « + »                     | 000000001357,28  |

| 6. Result of the first sum                                                | « = »                     | 000000001592,74  |

| 7. Store in first accumulator register                                    | « +I »                    | 000000001592,74  |

| 8. Enter third term 174,27                                                | « + »                     | 000000000174,27  |

| 9. Enter fourth term 459,96                                               | « + »                     | 000000000469,96  |

| 10. Result of the second sum                                              | « = »                     | 000000000634,23  |

| 11. Subtract second sum from first                                        | « –I »                    | 000000000634,23  |

| 12. Enter minuend 547,54                                                  | « + »                     | 000000000547,54  |

| 13. Enter subtrahend 2375,49                                              | «—»                       | 000000002375,49- |

| 14. Result of the third sum                                               | « = »                     | 000000001827,95- |

| 15. Add the result from the MR register to the first accumulator register | « 1+ »                    | 000000001827,95– |

| 16. Display the final result of the calculation                           | « +I »                    | 000000000869,44– |

It is evident from the above examples that algebraic calculation of Addition and Subtraction with sign is accomplished by the arithmetic-logic unit of the machine.

# **1.2.3.** Multiplication.

Multiplication is carried out by arithmetic-logic unit with the result stored in the operational register MR. To complete the operation in the specific sequence the function keys « X » and « = » are used. The result, found in the operational register MR, can be stored in the three accumulator registers by pressing the function keys « +I », « +II », « +II », « -I », « -II », « -III », a consequence of which adds or subtracts the result to the current information in the accumulator registers.

The process of completing the multiplication automatically rounds off the result at the last step.

| Order of operation                                  | Function key | Display          |

|-----------------------------------------------------|--------------|------------------|

| 1. Erase the operational registers                  | « Lö »       | 0000000000000000 |

| 2. Decimal point switch setting                     | «4»          | 0000000000,0000  |

| 3. Enter the multiplicand 125,25                    | « X »        | 0000000125,2500  |

| 4. Enter the multiplier 15,25 and obtain the result | « = »        | 00000001910,0625 |

Example 10. **a**  $\mathbf{x} \mathbf{b} = \mathbf{c}$  125,25 x 15,25 = 1910,0625

Example 11. **a**  $\mathbf{x} \mathbf{b} = \mathbf{c}$  123,12 x 0,51 = 62,7912

| Order of operation                                | Function key | Display          |

|---------------------------------------------------|--------------|------------------|

| 1. Erase the operational registers                | « Lö »       | 0000000000000000 |

| 2. Decimal point switch setting                   | « 2 »        | 0000000000000,00 |

| 3. Enter the multiplicand 123,12                  | «X»          | 000000000123,12  |

| 4. Enter the multiplier ,51 and obtain the result | « = »        | 0000000000062,79 |

The position of the decimal point switch is determined by the required degree of accuracy of the calculation or by the sum of the number of decimal digits of the factors.

| Example 12. | $\mathbf{a} \mathbf{x} \mathbf{b} \mathbf{x} \mathbf{c} = \mathbf{z}$ | 23,5 x 12,5 x 2,12 = 622,75 |

|-------------|-----------------------------------------------------------------------|-----------------------------|

|-------------|-----------------------------------------------------------------------|-----------------------------|

| Order of operation                                     | Function key | Display          |

|--------------------------------------------------------|--------------|------------------|

| 1. Erasure of operational registers                    | « Lö »       | 0000000000000000 |

| 2. Decimal point switch setting                        | « 2 »        | 000000000000,00  |

| 3. Enter first factor23,5                              | « X »        | 000000000023,50  |

| 4. Enter second factor 12,5 and obtain the result      | « = »        | 000000000293,75  |

| 5. Prepare for multiplication by the third factor      | «X»          | 000000000293,75  |

| 6. Enter the third cofactor 2,12 and obtain the result | « = »        | 000000000622,75  |

The operational capabilities of the machine make it possible to perform multiplication with the use of constants.

An example of multiplication with a constant coefficient is examined below.

| Example 13. | $a \ge b = c$ | 125 x 5,3 = 622,5    |

|-------------|---------------|----------------------|

|             | d x b = z     | 15,36 x 5,3 = 81,408 |

| Order of operation                 | Function key              | Display                                 |

|------------------------------------|---------------------------|-----------------------------------------|

| 1. Erase accumulator registers     | « *I », « *II », « *III » |                                         |

| 2. Erase the operational registers | « Lö »                    | 000000000000000000000000000000000000000 |

| 3. Decimal point switch setting    | « 2 »                     | 0000000000000,00                        |

| 4. Enter constant factor 5,3       | $\ll X^N \gg$             | 000000000005,30                         |

| 5. Enter first factor 125,         |                           | 000000000012,50                         |

| 6. Result                          | $\ll X^N \gg$             | 000000000622,50                         |

| 7. Enter second factor 15,36       |                           | 000000000015,36                         |

| 8. Result                          | $\ll X^N \gg$             | 000000000081,41                         |

The calculation of sum or difference products is carried out with use of one of the accumulator registers.

# Example 14. (a x b) + (c x d) = z(25 x 10,3) + (17,2 x 5,1) = 345,22

| Order of operation                                          | Function key              | Display          |

|-------------------------------------------------------------|---------------------------|------------------|

| 1. Erase accumulator registers                              | « *I », « *II », « *III » |                  |

| 2. Erase the operational registers                          | « Lö »                    | 0000000000000000 |

| 3. Decimal point switch setting                             | «1»                       | 00000000000000,0 |

| 4. Enter first factor 25,                                   | « X »                     | 0000000000025,0  |

| 5. Enter second factor 12,5 and obtain the result           | « = »                     | 0000000000257,5  |

| <ol> <li>Store result in an accumulator register</li> </ol> | « +I »                    | 0000000000257,5  |

| 7. Enter third factor 17,2                                  | « X »                     | 0000000000017,2  |

| 8. Enter fourth factor 5,1 and obtain the result            | « = »                     | 0000000000087,7  |

| 9. Add first and second products                            | « +I »                    | 0000000000087,7  |

| 10. Result                                                  | « *I »                    | 000000000345,2   |

The calculation of a difference in two products (a x b) - (c x d) = x, is carried out in a sequence, analogous to the calculation of the sum of two products, with a difference, such that in point 9 of example 14 press the  $\ll$  -I » key instead of the  $\ll$  +I » key.

In the case of the negative value of cofactors, after the entry of a multiplicand or coefficient the key for the entry of negative values is used. The arithmetic-logic unit of machine accomplishes the operation of multiplication taking into account the signs of cofactors.

Example 15.  $(-a) \times (-b) = +c$  $(-24,5) \times (-3,75) = 91,875.$

| Order of operation                 | Function key | Display          |

|------------------------------------|--------------|------------------|

| 1. Erase the operational registers | « Lö »       | 000000000000000  |

| 2. Decimal point switch setting    | « 2 »        | 0000000000000000 |

Continuation

| Order of operation                                     | Function key | Display            |

|--------------------------------------------------------|--------------|--------------------|

| 3. Enter first factor 24,5<br>Negate value key « -# »  | « X »        | 000000000024,50 -  |

| 4. Enter second factor 3,75<br>Negate value key « -# » | «—»          | 000000000003,75-   |

| 5. Result                                              | « = »        | 0000000000091,88 - |

Operation (a) x(-b) = -c is carried out in a similar manner to that in example 15 and is characterized by the fact that after the entry of the first factor the negate entry key « -# » is not used. The calculation of the signs of cofactors is accomplished by the arithmetic-logic unit of the machine of the operation of algebraic multiplication.

# **1.2.4.** Exponentiation.

Exponentiation is carried out by the arithmetic-logic unit with storage of the result in the operative register MR. For performance of the operation in the specific sequence the functional keys « X » and « X<sup>n</sup> » are provided. The result in register MR can be stored in the accumulating registers AC1 - AC3 by pressing the corresponding « +I », « +II », « +II », « -I », « -III »

| Order of operation                  | Function key           | Display          |

|-------------------------------------|------------------------|------------------|

| 1. Erasure of operational registers | « Lö »                 | 0000000000000000 |

| 2. Decimal point switch setting     | « 0 »                  | 0000000000000000 |

| 3. Entry of the number 25           | « X »                  | 000000000000025  |

| 4. Result of 25 squared             | $\ll X^n \gg$          | 000000000000625  |

| 5. Result of 25 cubed               | $\ll X^n \gg$          | 00000000015625   |

| 6. Result of 25 quadrupled          | $\ll \mathbf{X}^n \gg$ | 00000000390625   |

With the erection of the negative number into the degree with the even index the result of calculation is positive. With the erection of the negative number into the degree with the odd index the result of calculation is negative.

# 1.2.5. Division.

Division is carried out by the arithmetic-logic unit with the result stored in the operational MR register. To complete the operation in the specific sequence the function keys  $\ll : \gg, \ll = \gg$  are used. The result, found in the operational register MR, can be stored in the three accumulator registers by pressing the function keys  $\ll +I \gg, \ll +II \gg, \ll +III \gg, \ll -II \gg, \ll -III \gg, \ll -III \gg, \approx -III \gg$ , a consequence of which adds or subtracts the result to the current information in the accumulator registers.

In the process of completing the division operation the quotient is automatically rounded off in the last step.

#### Example 17. $\mathbf{a} : \mathbf{b} = \mathbf{c}$ 625 : 5 = 125

| Order of operation                       | Function key | Display          |

|------------------------------------------|--------------|------------------|

| 1. Erasure of operational registers      | « Lö »       | 0000000000000000 |

| 2. Decimal point switch setting          | « 0 »        | 0000000000000000 |

| 3. Enter dividend 625                    | «:»          | 000000000000625  |

| 4. Enter divisor 5 and obtain the result | « = »        | 00000000000125   |

The operational capabilities of machine make it possible to perform the operation of division with the use of constants of dividend and divisor.

| Example 18. | $\mathbf{d}:\mathbf{b}=\mathbf{c}$     | 143,15 : 8 = 17,89375 |

|-------------|----------------------------------------|-----------------------|

|             | $\mathbf{a} : \mathbf{b} = \mathbf{z}$ | 247,232:8=30,904      |

| Order of operation                 | Function key              | Display          |

|------------------------------------|---------------------------|------------------|

| 1. Erase accumulator registers     | « *I », « *II », « *III » |                  |

| 2. Erase the operational registers | « Lö »                    | 0000000000000000 |

| 3. Decimal point switch setting    | « 3 »                     | 000000000000,000 |

| 4. Enter first dividend 143,15     | «:»                       | 00000000143,150  |

| Order of operation                | Function key | Display         |

|-----------------------------------|--------------|-----------------|

| 5. Enter divisor constant 8,      | « +I »       | 00000000008,000 |

| 6. Result of first sum            | « = »        | 00000000017,894 |

| 8. Enter second dividend 247,232  | «:»          | 00000000247,232 |

| 9. Return result of the first sum | «▼I»         | 00000000008,000 |

| 4. Final result                   | « = »        | 00000000030,904 |

The position of the decimal point switch is determined by the required degree of accuracy or by the larger number of decimal points from the numbers entered for division.

# Example 19. **a** : **d** = **z** 1235,43 : 26 = 47,5265 **a** : **b** = **c** 1235,43 : 47 = 26,2857

| Order of operation                         | Function key              | Display          |

|--------------------------------------------|---------------------------|------------------|

| 1. Erase accumulator registers             | « *I », « *II », « *III » |                  |

| 2. Erase the operational registers         | « Lö »                    | 0000000000000000 |

| 3. Decimal point switch setting            | « 2 »                     | 0000000000000,00 |

| 4. Enter constant dividend 1235,43         | « +I »                    | 000000001235,43  |

| 5. Prepare for division                    | «:»                       | 000000001235,43  |

| 6. Enter divisor 26, and obtain the result | « = »                     | 000000000047,52  |

| 7. Indication of dividend                  | « ▼I »                    | 000000001235,43  |

| 8. Prepare for division                    | «:»                       | 000000001235,43  |

| 9. Enter divisor 47, and obtain the result | « = »                     | 000000000026, 29 |

The calculation of sum or difference of the quotients is carried out with use of one of the accumulator registers.

# Example 20. $(\mathbf{a} : \mathbf{b}) - (\mathbf{c} : \mathbf{d}) = \mathbf{z}$ (5625 : 25) - (1234 : 24) = 173,58.

| Order of operation                         | Function key              | Display          |

|--------------------------------------------|---------------------------|------------------|

| 1. Erase accumulator registers             | « *I », « *II », « *III » |                  |

| 2. Erase the operational registers         | « Lö »                    | 0000000000000000 |

| 3. Decimal point switch setting            | « 2 »                     | 000000000000,00  |

| 4. Enter first sum dividend 5625,          | «:»                       | 000000005625,00  |

| 5. Enter divisor 25, and obtain the result | « = »                     | 000000000225,00  |

| 6. Store result in accumulator register    |                           | 000000000225,00  |

| 7. Enter second sum dividend 1234,         | «:»                       | 000000001234,00  |

| 8. Enter divisor 24, and obtain the result | « = »                     | 000000000051,42  |

| 9. Subtract second result the from first   | « -I »                    | 000000000051,42  |

| 10. Display the result                     | « *I »                    | 000000000173,58  |

The calculation of the sum of two quotients is carried out in a sequence, analogous to the calculation of a difference in two quotients. The difference is to press the functional key  $\ll +I \gg$ , instead of  $\ll -I \gg$  (point 9 of example 20).

For negative value dividends and divisors press the negate value key « -# » after entering the dividend. Division is carried out taking into account the signs of the dividend and divisor.

Example 21. (-a) : (-b) = c (-3174,6) : (-13) = 244,2

| Order of operation                                  | Function key | Display          |

|-----------------------------------------------------|--------------|------------------|

| 1. Erase the operational registers                  | « Lö »       | 0000000000000000 |

| 2. Decimal point switch setting                     | « 1 »        | 00000000000000,0 |

| 3. Enter dividend 3174,6<br>Negate value key « -# » | «:»          | 000000003174,6   |

| 4. Enter divisor 13,<br>Negate value key « -# »     | « +I »       | 0000000000013,0  |

| 5 Result                                            | « = »        | 0000000000244,2  |

The calculation of the signs of the dividend and divisor is accomplished by the arithmetic-logic unit of the machine of the operation of algebraic division.

# **1.2.6.** Extraction of square root.

In normal operation of the computer there is no facility for the automatic extraction of square roots. In this case the most convenient method for the extraction of a square root is to use the sequential approximation method.

For the expression  $y_n + 1 = 0.5 \left( \frac{x}{y_n} + y_n \right)$ , where an accurate result is usually found after the third

approximation.

Prior to the beginning of calculation the radicand should be broken on the verge of two numbers to the left from the decimal point. The quantity of sides defines quantity of categories of the whole part of a root. In the first approximation, the root is evaluated according to the left face, in which there can be one number.

In the process of calculation to increase the accuracy of the result it is desirable to perform intermediate operations with the largest possible quantity of the decimal digits.

Example 22.

$$\sqrt{985,96} = 31,4.$$

Root from 9 composes 3. Two faces of the integer part of radicand X give the two-digit number of  $y_n = 30$ .

The result of the first approximation will be:

$$\frac{0.5 \times 985,96}{30} + 30 = 31,432667$$

(Checking: 31,432667<sup>2</sup> = 988,012555);

The result of the second approximation

$\frac{0.5 \times 985,96}{31,432667} + 31,432667 = 31,400017$

(Checking: 31,400017<sup>2</sup> = 985,961068);

The result of the third approximation

$\frac{0.5 \times 985,96}{31,400017} + 31,400017 = 31,400000$

(Checking:  $31,4^2 = 985,96$ ).

| Order of operation                                                    | Function key              | Display                                 |

|-----------------------------------------------------------------------|---------------------------|-----------------------------------------|

| 1. Erase accumulator registers                                        | « *I », « *II », « *III » |                                         |

| 2. Erase the operational registers                                    | « Lö »                    | 000000000000000000000000000000000000000 |

| 3. Decimal point switch setting                                       | « 6 »                     | 00000000,000000                         |

| 4. Enter dividend 985,96                                              | « +I »                    | 000000985,960000                        |

| 5. Prepare for Division                                               | «:»                       | 000000985,960000                        |

| 6. Enter divisor 30,                                                  | « +II »                   | 00000030,000000                         |

| 7. Result of quotient                                                 | « = »                     | 00000032,865333                         |

| 8. Add to accumulator register 2                                      | « +II »                   | 000000032,865333                        |

| 9. Result                                                             | « *I »                    | 00000062,865333                         |

| 10. Prepare for Division                                              | «:»                       | 000000062,865333                        |

| 11. Enter divisor 2, Result of the first approximation                | « = »                     | 000000031,432667                        |

| 12. Store the result into accumulator register                        | « +II »                   | 000000031,432667                        |

| 13. Recall to the operational register<br>and show result of dividend | « ▼I »                    | 000000985,960000                        |

| 14. Prepare for Division                                              | «:»                       | 000000985,960000                        |

| 15. Recall to the operational register and show result of dividend    | «▼II »                    | 000000031,432667                        |

| 16. Result                                                            | « = »                     | 000000031,367367                        |

| 17. Add to accumulator register 2                                     | « +II »                   | 000000031,367367                        |

| 18. Result                                                            | « *II »                   | 000000062,800034                        |

| 19. Prepare for Division                                              | «:»                       | 000000062,800034                        |

| 20. Enter divisor 2, Result of the first approximation                | « = »                     | 000000031,400017                        |

| 21. Add to accumulator register 2                                     | « +II »                   | 000000031,400017                        |

| 22. Recall to the operational register and show result of dividend    | « ▼I »                    | 000000985,960000                        |

| 23. Prepare for Division                                              | «:»                       | 000000985,960000                        |

| Order of operation                         | Function key  | Display          |

|--------------------------------------------|---------------|------------------|

| 24. Recall accumulator 2, Divide           | « ▼II »       | 00000031,400017  |

| 25. Quotient result                        | « = »         | 00000031,399983  |

| 26. Add                                    | « +II »       | 00000031,399983  |

| 27. Result                                 | « *II »       | 00000062,800000  |

| 28. Division                               | «:»           | 00000062,800000  |

| 29. Enter divisor 2, and obtain the result | « = »         | 00000031,400000  |

| 30. Result of the third approximation      | « X »         | 000000031,400000 |

| 31. Checking                               | $\ll X^n \gg$ | 000000985,960000 |

# **1.2.7.** Examples of the completion of complex calculations.

# Example 23, **a** $\mathbf{x}$ (**b** + **c** - **d**) = $\mathbf{z}$ 123,15 $\mathbf{x}$ (6,4 + 31 - 0,75) = 4513,4475.

| Order of operation                 | Function key | Display          |

|------------------------------------|--------------|------------------|

| 1. Erase the operational registers | « Lö»        | 000000000000000  |

| 2. Decimal point switch setting    | « 2 »        | 000000000000,00  |

| 3. Enter multiplicand 123,15       | « X »        | 000000000123,15  |

| 4. Enter the first term 6,4        | « + »        | 000000000006,40  |

| 5. Enter second term of 31,        | « + »        | 000000000031,00  |

| 6. Enter subtrahend 75             | « - »        | 000000000000,75- |

| 7. Result                          | « = »        | 000000004513,45  |

# Example 24. $\mathbf{a} : (\mathbf{b} + \mathbf{c} - \mathbf{d}) = \mathbf{z}$ 1127: (25,471 + 31,74 - 7,15) = 22 51311

| Order of operation                 | Function key | Display          |

|------------------------------------|--------------|------------------|

| 1. Erase the operational registers | « Lö»        | 0000000000000000 |

| 2. Decimal point switch setting    | « 3 »        | 00000000000,000  |

| 3. Enter dividend 1127,            | «:»          | 00000001127,000  |

# Continuation

| Order of operation      |        | Function key | Display           |

|-------------------------|--------|--------------|-------------------|

| 4. Enter the first term | 25,471 | « + »        | 00000000025,471   |

| 5. Enter second term    | 31,74  | « + »        | 00000000031,740   |

| 6. Enter subtrahend     | 7,15   | «—»          | 000000000007,150- |

| 7. Result               |        | « = »        | 00000000022,513   |

Example 25.  $(\mathbf{a} \mathbf{x} \mathbf{b}) : \mathbf{c} = \mathbf{z}$  $(125 \times 25): 7,3 = 428,0821$

| Order of operation                         | Function key | Display         |

|--------------------------------------------|--------------|-----------------|

| 1. Erasure of operational registers        | « Lö »       | 000000000000000 |

| 2. Decimal point switch setting            | « 2 »        | 000000000000,00 |

| 3. Enter the first cofactor 125,           | « X »        | 000000000126,00 |

| 4. Enter second cofactor 25,               | « = »        | 000000003125,00 |

| 5. Division                                | «:»          | 000000003125,00 |

| 6. Enter divisor 7,3 and obtain the result | « = »        | 000000000428,08 |

Example 26.

$$\frac{a \times b}{c} - \frac{d \times l}{y} = z$$

$$\frac{135 \times 3,7}{2,4} - \frac{35 \times 27,3}{12} = 128,50$$

| Order of operation                  | Function key              | Display          |  |

|-------------------------------------|---------------------------|------------------|--|

| 1. Erasure of accumulator registers | « *I », « *II », « *III » |                  |  |

| 2. Erasure of operational registers | « Lö »                    | 000000000000000  |  |

| 3. Decimal point switch setting     | « 2 »                     | 0000000000000,00 |  |

| 4. Enter cofactor 135,23            | « = »                     | 000000003125,00  |  |

| Order of operation                               | Function key | Display         |  |

|--------------------------------------------------|--------------|-----------------|--|

| 5. Enter cofactor 3,7<br>and obtain the result   | « = »        | 000000000499,50 |  |

| 6. Divide                                        | «:»          | 000000000499,50 |  |

| 7. Enter divisor 2,4<br>and obtain the result    | « = »        | 000000000208,13 |  |

| 8. Store quotient to accumulator 1               | « +I »       | 000000000208,13 |  |

| 9. Enter cofactor 35,                            | « X »        | 00000000035,00  |  |

| 10. Enter cofactor 27,3<br>and obtain the result | « = »        | 000000000955,50 |  |

| 11. Division                                     | «:»          | 000000000955,50 |  |

| 12. Enter divisor 12,<br>and obtain the result   | « = »        | 000000000079,63 |  |

| 13. Subtract                                     | « – I »      | 000000000079,63 |  |

| 14. Calculation result                           | « *I »       | 000000000128,50 |  |

The calculation of  $\frac{a \times b}{c} = \frac{d \times l}{y} = z$  is carried out in the sequence of the given example above but is characterized by the fact that in point 13 instead of using the Subtraction from accumulator key « -I », the Add to accumulator key « +I » is used.

## **Chapter II**

# **ELEMENTS of pulse TECHNIQUE AND POWER SUPPLY**

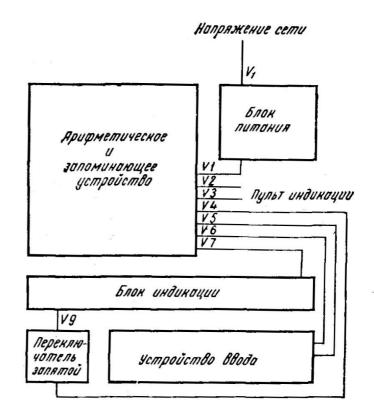

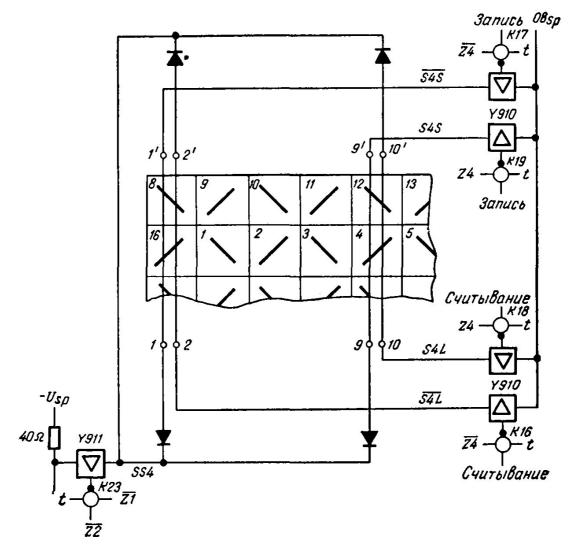

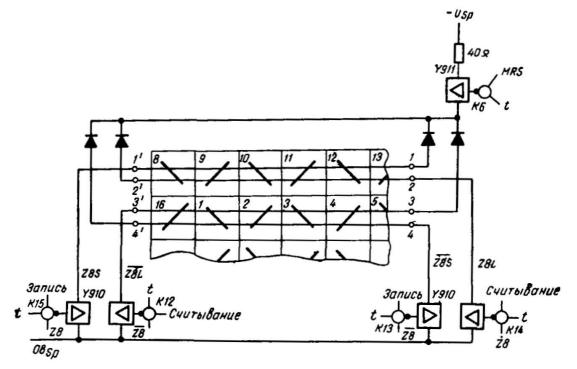

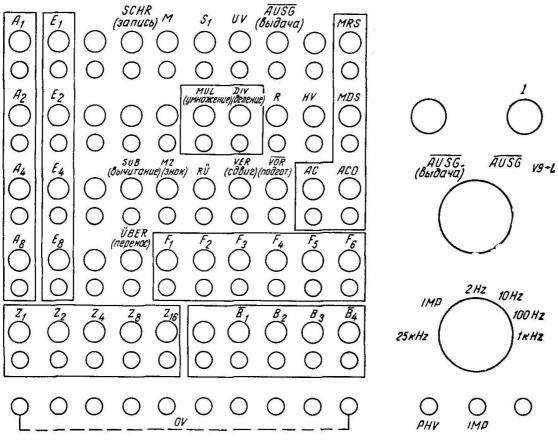

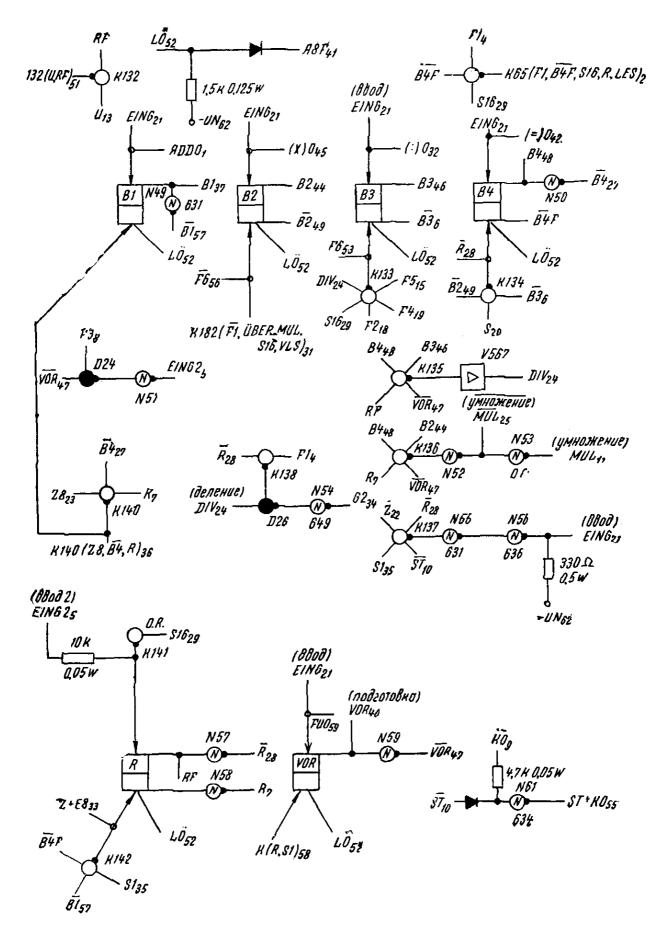

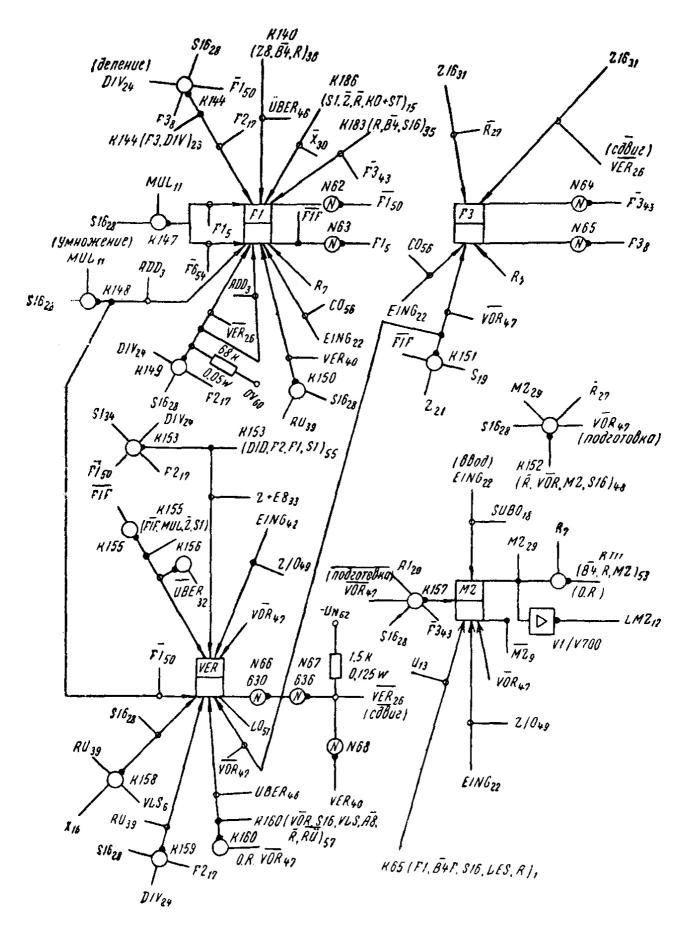

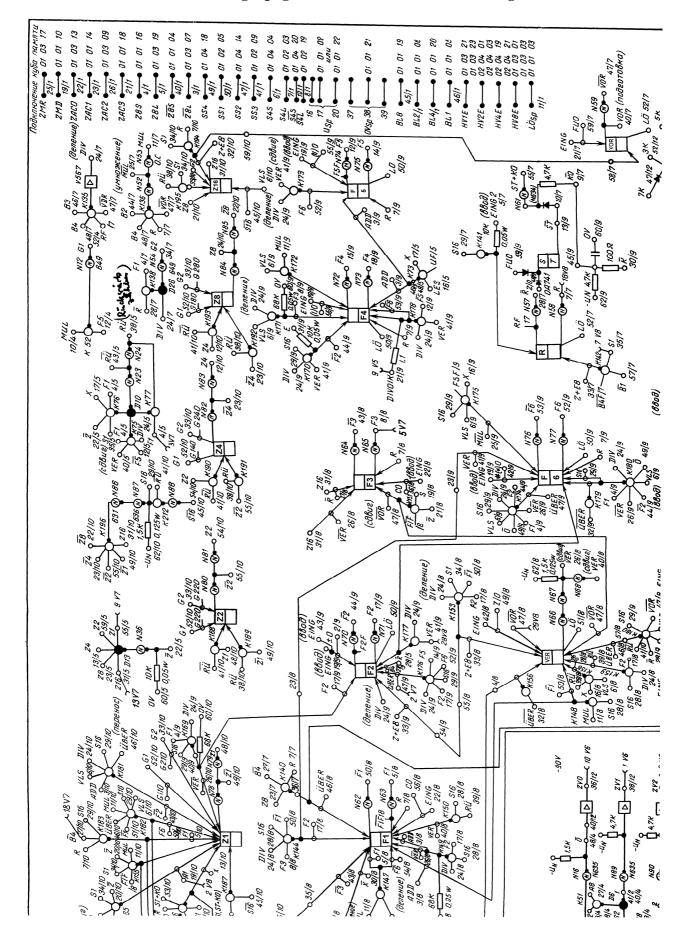

# II. 1. BLOCK DIAGRAM OF THE MACHINE.

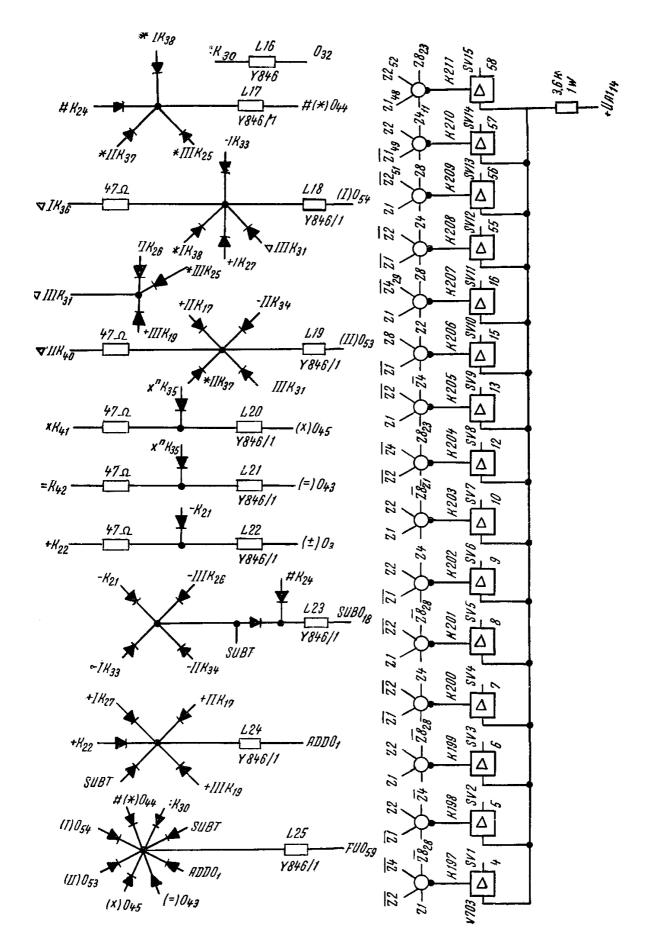

All necessary information enters the arithmetical and storage unit by pressing the appropriate keyboard digital and functional keys in a specific sequence (Fig. 2).

The entry of digital information for the completion of arithmetic operations and different calculations is ensured by the decimal digital keyboard.

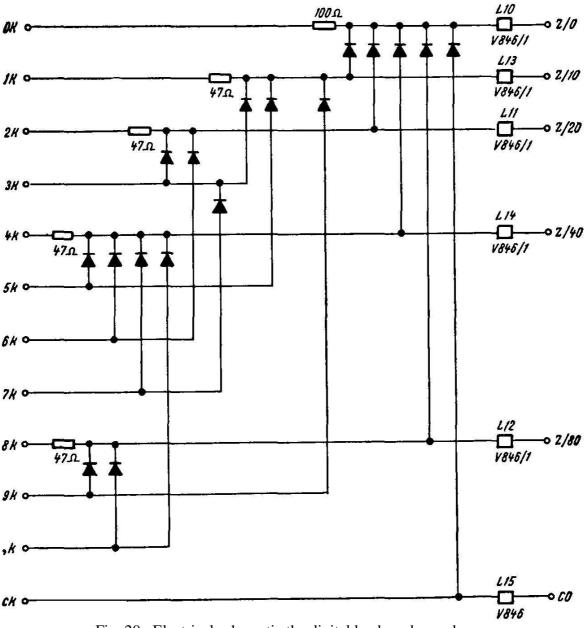

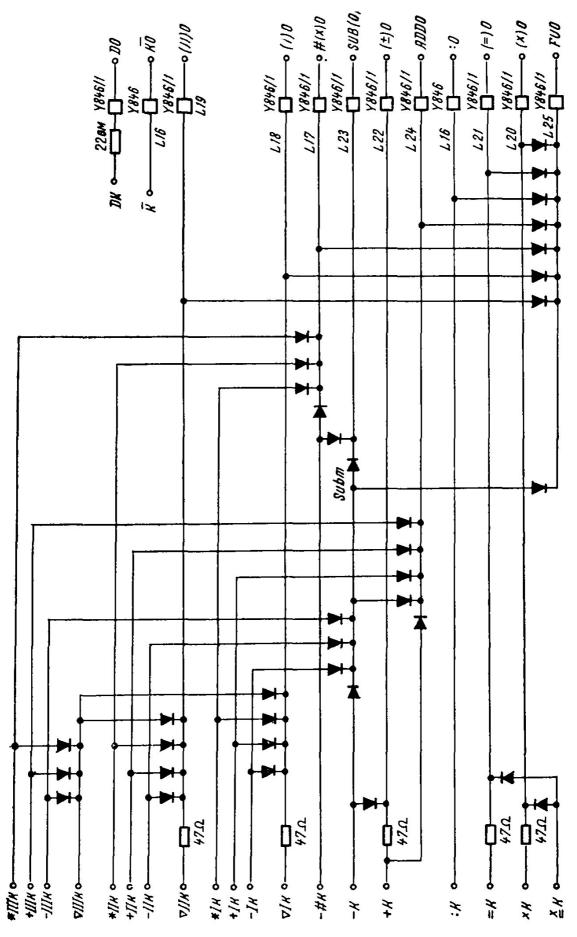

The encoding of the input information encodes the inputted digital information from the keyboard from the decimal system into the Binary Coded Decimal numeration system.

The coded digital information from the encoder output is in proportion to the collection.

The entered number is passed to the arithmetic-logic unit and is stored in the appropriate part of the ferrite core memory in the operational register MR.

The management teams and

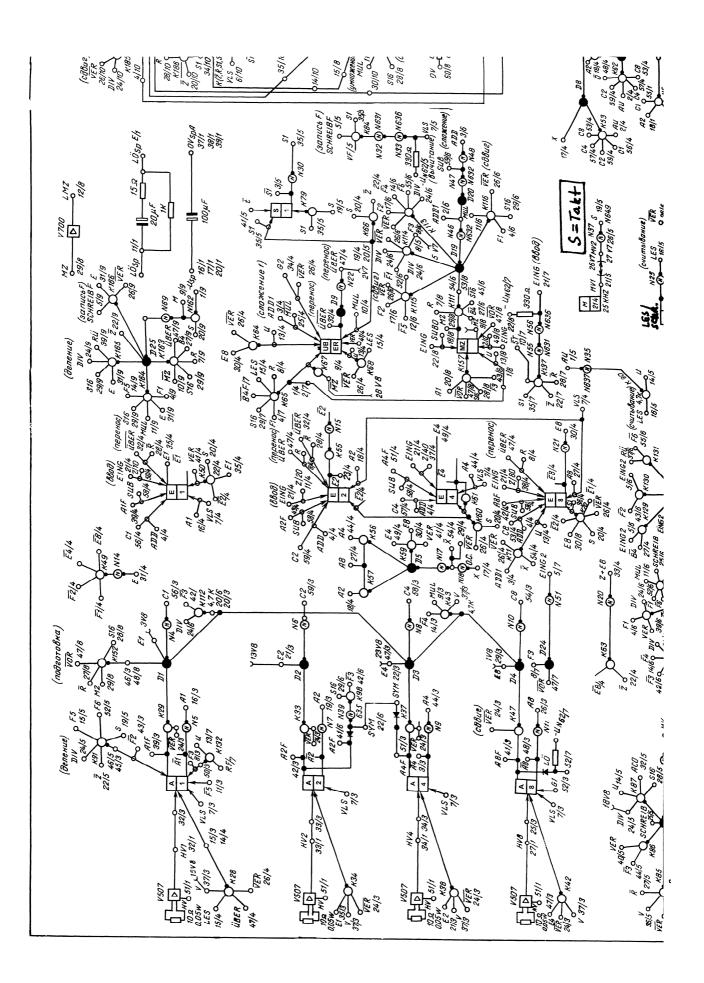

Fig. 2. Block diagram of a « Soemtron-220 » computer.

arithmetic operations are carried out the functional keys for input unit. Pressing one of the functional keys causes the completion of the corresponding operation in the arithmetic-logic unit.

All operations in the machine are stored in the ferrite core memory as digital information and are performed in the Binary Coded Decimal numeration system.

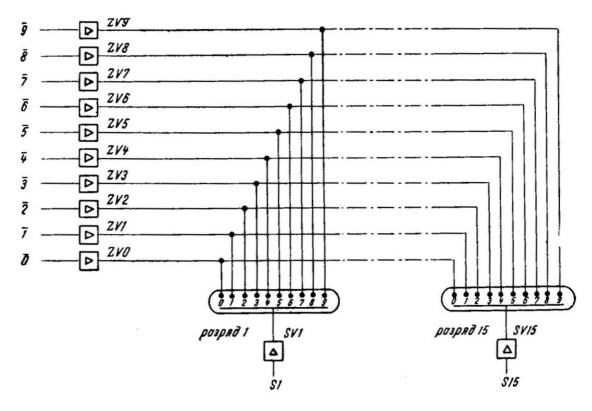

The information, written into the four core planes of the MR register by the decoder of arithmetic-logic unit, is transferred from the binary coded decimal numeration system into decimal, the decoded digital information from the output of the decoders is shown by the luminous digital lamps of display unit, which ensures the visual output of the entered information, results of arithmetic operations and different calculations in the decimal system. For visual output of the digital information of the accumulator registers, the appropriate functional keys are used, which ensure the storage of the digital information of the accumulating register into the operational register MR.

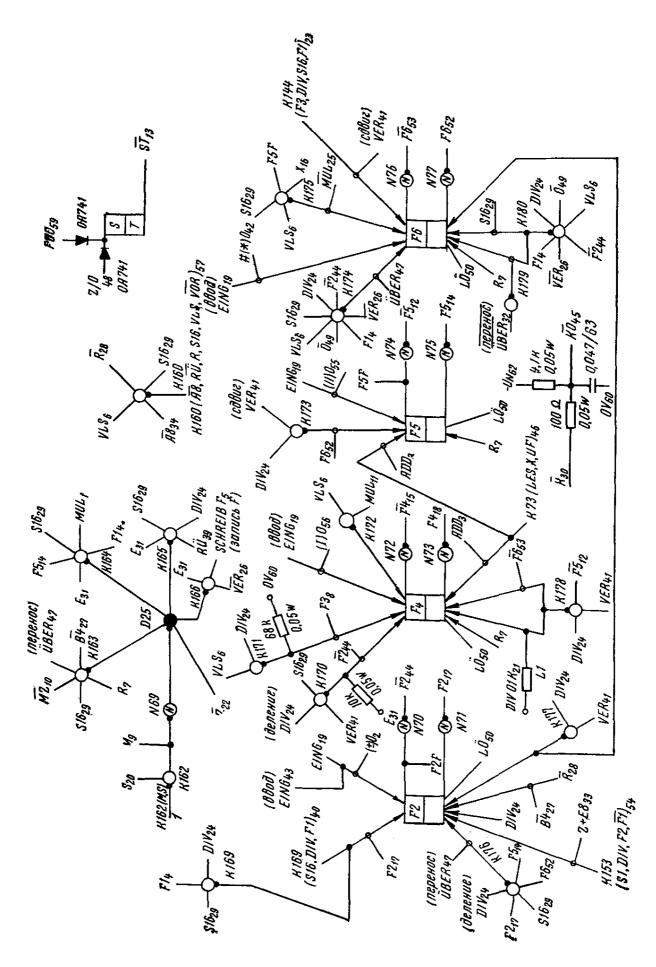

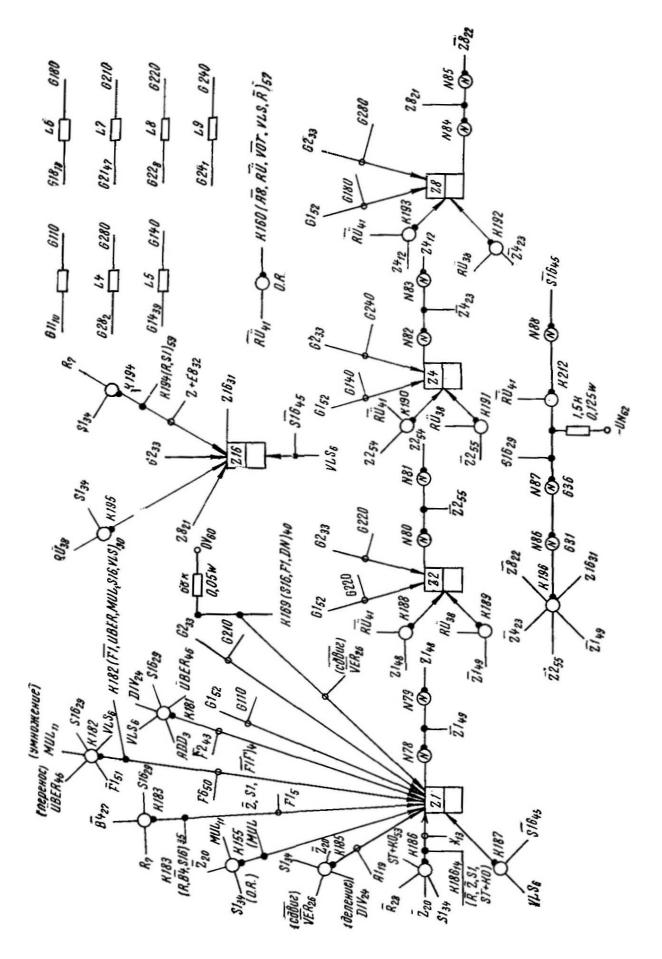

# II.2. ARITHMETIC-LOGIC UNIT

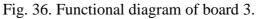

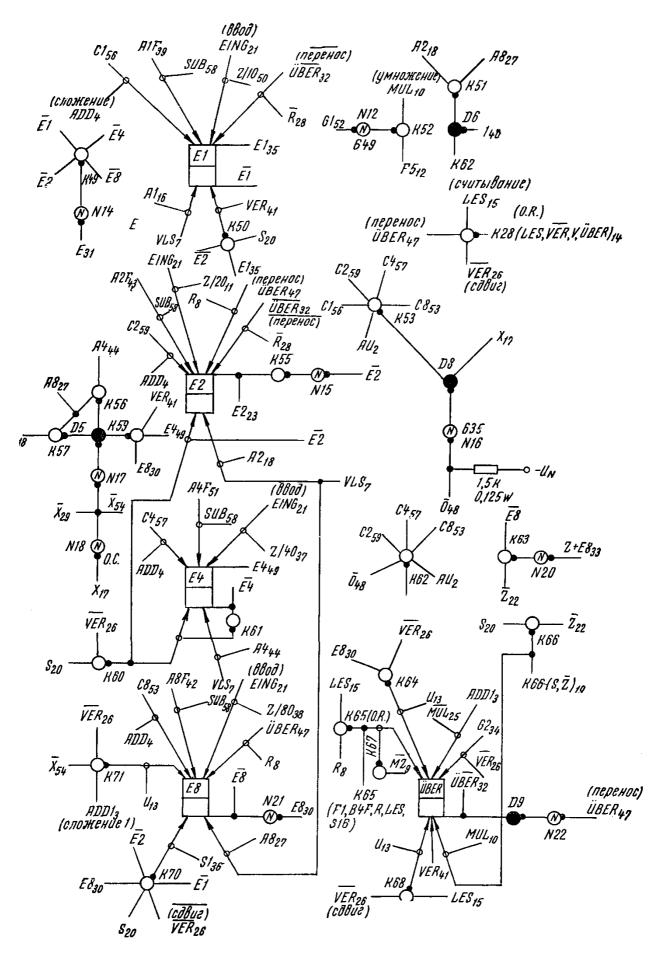

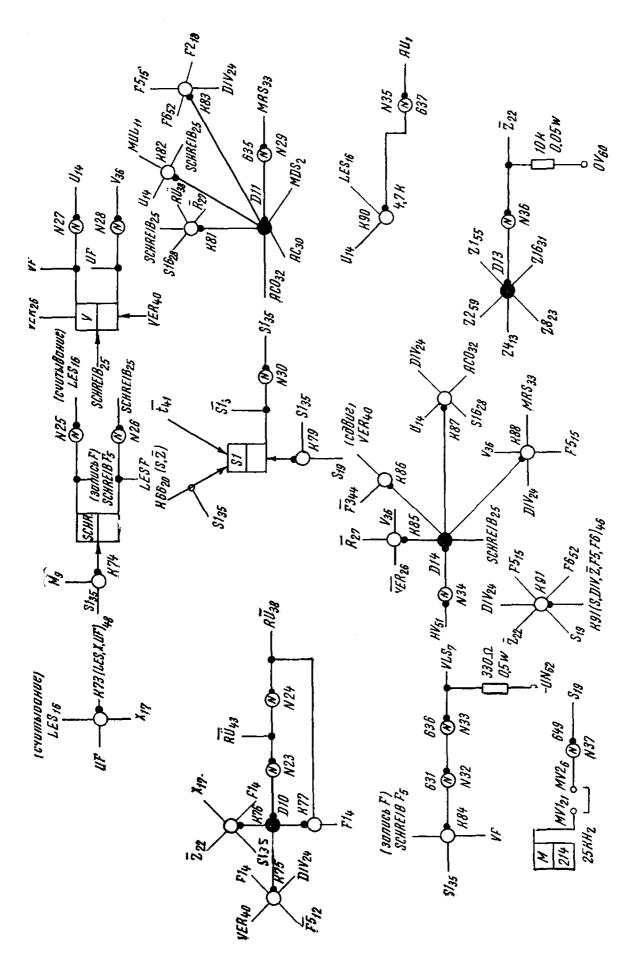

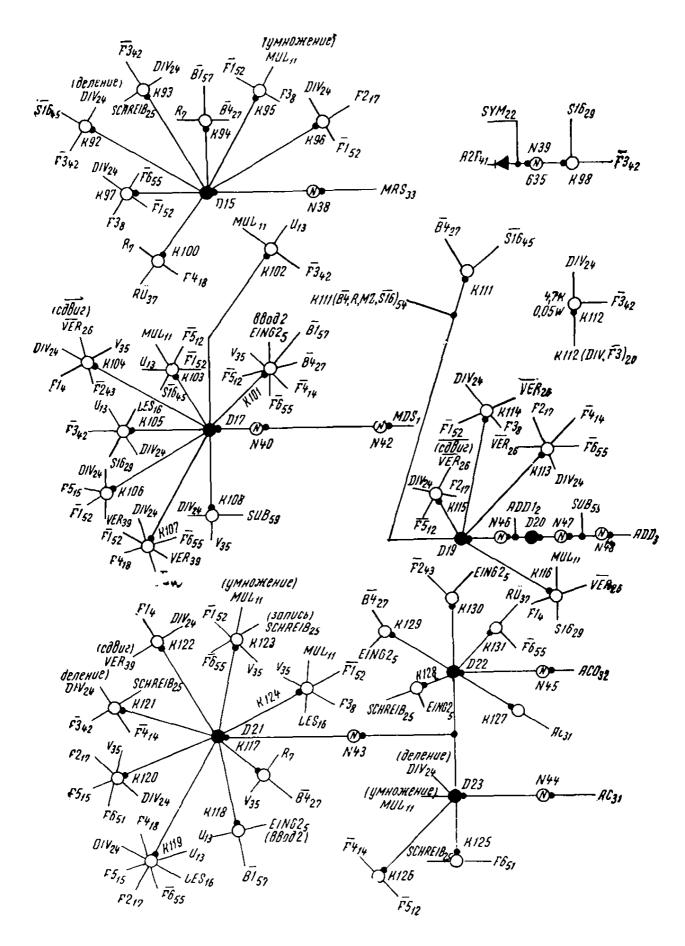

The arithmetic-logic unit consists of 12 boards of printed circuit assemblies with the attached elements of the required electronic circuits, which accomplish different arithmetic operations and calculations.

The diagrams used show the logic functions, switching, memory and amplifier elements of the overall diagram of the arithmetic-logic unit of the computer. Signals formed at the outputs, and also those entering the inputs of the corresponding electronic circuits must be within the limits from 0V to -12V. With exception are the signals, which are formed by the anode and cathode amplifier circuits for the display.

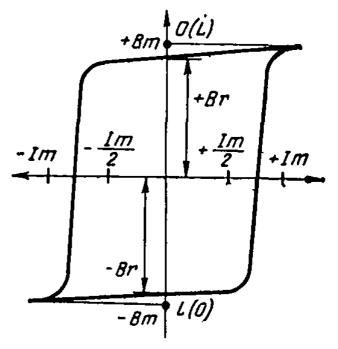

It is customary that those signals entering the inputs or formed at outputs of the corresponding electronic circuits, in the voltage range from 0V to -1,5V are assumed to be a logic 0 signal. Voltages in the range from -8V to -12V are assumed to be a logic 1 signal.

The arithmetic-logic unit through appropriate connectors is connected to the power unit, input unit, display unit and decimal point position switch circuits to make the overall electrical diagram of machine.

On the basis of a number of the design features of machine, the memory unit is considered as separate unit in the composition of arithmetic-logic unit.

**Note.** In the schematic circuits, transistor part numbers indicated in brackets were those established and used in the appropriate schematics of units and elements of the machines of the first releases.

# 11.3. ELEMENTS OF THE FUNCTIONAL DIAGRAM.

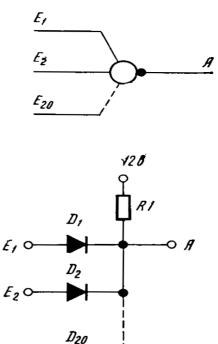

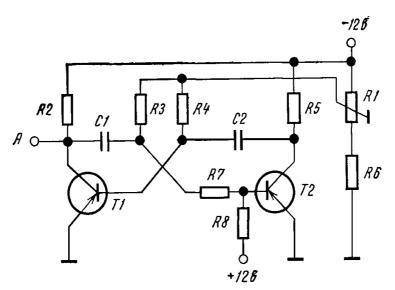

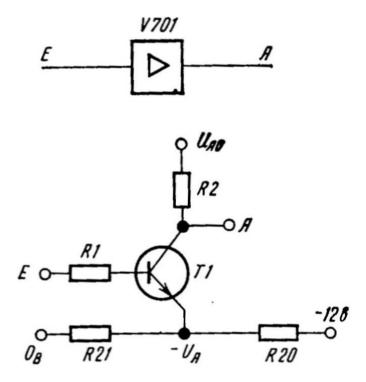

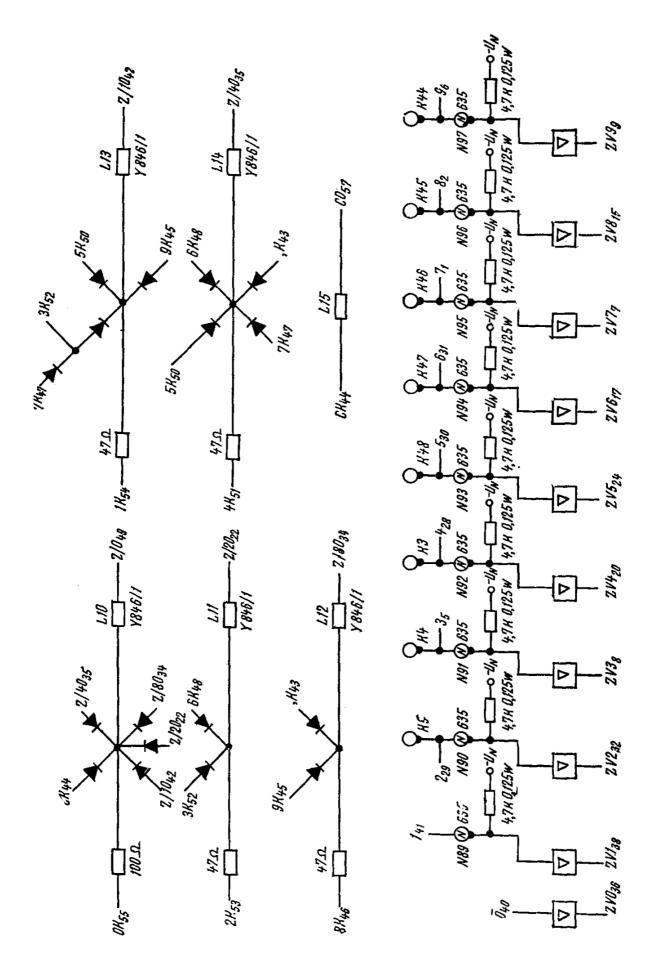

# **11.3.1. AND** gate (conjunction).

The diagram shows the logical function « AND », on conditions of which the logic 1 signal at output A of diagram is generated only when all inputs E enter logic 1 level signals. The correct realization of the logical function can only be executed when in the absence of logic 1 signals the appropriate inputs E of the gate enter logic 0 signals.

The diagram is drawn with semiconductor diodes and has one output and can have from 2 to 20 inputs.

On the overall functional diagram of the machine « AND » gates are given numbers from K1 to K211.

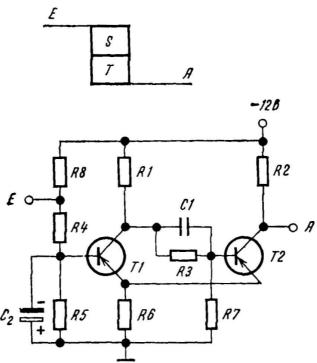

The logic symbol and schematic circuit diagram are given in Fig. 3.

An  $\ll$  AND  $\gg$  gate depending on signals at the inputs to E1 - E20 is in the closed or open state.

With all signals at logic 0 on the inputs E1 - E20 of an « AND » gate the diodes are forward biased or turned on resulting in a small forward voltage drop. Current in the circuit: 0V, parallel diodes D1 - D20, resistor R1, -12V - on the small resistance of the forward biased diodes creates an insignificant voltage drop. In essence a voltage drop occurs on the 10 kilohms resistor, therefore, at output A a logic 0 signal is generated, which determines the conducting state of « AND » gate.

With simultaneous logic 1 signals to the inputs of E1 - E20 the gate is opened, as a result at the « AND » output a logic 1 level signal is produced.

When one or several inputs E of the gate input signals, the diodes of the corresponding inputs are connected to inverse voltages, I.E. the diodes are forward biased by a logic 0 signal, from the output of one or several forward biased diodes, which ensure the conducting state of the circuit.

Simultaneously input all inputs diagrams logic 0 signals or 1 because of the fluctuations of signal amplitude from 0V to -1,5V and from -8V to -12V are not usually opened and they do not reverse bias all diodes.

At the output of the on or off circuit a logic 0 or 1 signal is generated of a smaller amplitude to all the input signals,

$E_{20}$

Network elements: resistor R1 = 10Kilohms; 0,05W; 10%; diodes D1..D20 =1N35 or GAZ17

which reverse biases all the remaining diodes. Signals with the smaller amplitude provides the conducting state of the corresponding diode and the current in the circuit of diagram, proportional to a potential difference of the input signal and source -12V. The completion of the assigned logical functions by an « AND » gate is ensured only when in the absence of logic 1 signals at the appropriate E inputs a logic 0 signal is input.

When the resistor of an « AND » gate instead of being connected to the power supply -12V is connected to the output of an inverter (I.E. flip-flop, the diagram of joining), the « AND » gate becomes dependent on the signal at output of an inverter, I.E. controlled by the signal from the output of an equivalent component. Consequently the resistor of the circuit diagram becomes a control input.

The input of a logic 0 signal at this input blocks the function of the circuit. Input of a logic 1 signal at this input of the « AND » gate does not change the assigned logical functions. This practical control input can be considered as an additional input of an « AND » gate.

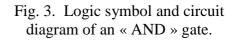

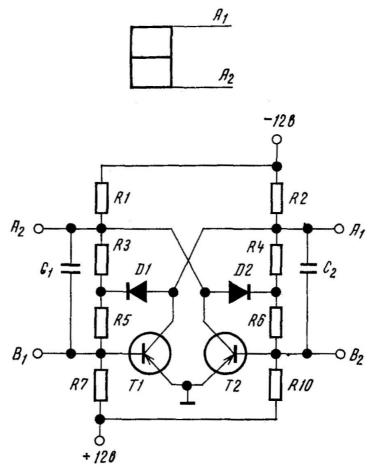

## **II.3.2.** OR gate (disjunction).

The diagram shows the logical function « OR », on conditions of which a logic 1 signal at output A is generated when one or several inputs E enters a logic 1 signal.

Fig. 4. Logic symbol and circuit diagram of an « OR » gate.

Network elements: Diodes D1 ..D20 - 1N35 or GAZ17.

The circuit is drawn with semiconductor diodes and has one output and can have from 2 to 20 inputs. The quantity of diodes in the diagram is determined by the quantity of inputs. The anodes of the diodes are connected to a common point and is the output of the circuit.

In the overall functional diagram of the machine « OR » gates are given gate numbers from D1 to D26. The logic symbol and schematic circuit diagram are given in Fig. 4.

The completion of logical functions by an « OR » gate does not require special circuit conditions, I.E. the connection of 0 logic signals or the presence or absence of logic 1 signals at the inputs of E1 - E20 of the gate. In a number of cases the inputs E of the gate a logic 0 signal is not input.

When one or several inputs simultaneously input logic 1 signals, the corresponding diodes are forward biased, as a result of which a logic 1 signal is output at point A of the gate. With the larger amplitude of all input signals, which reverse biases the remaining diodes of the gate. In

most cases the small resistance of the forward biased diode does not need to be considered.

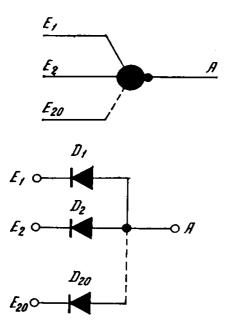

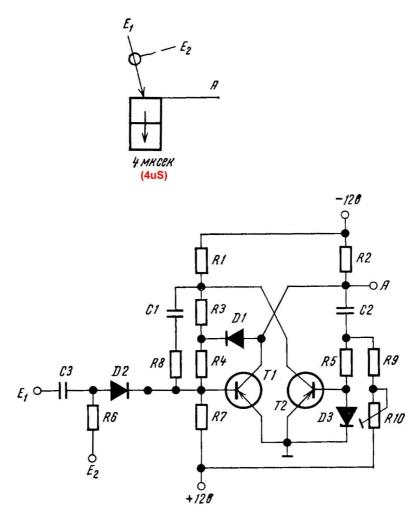

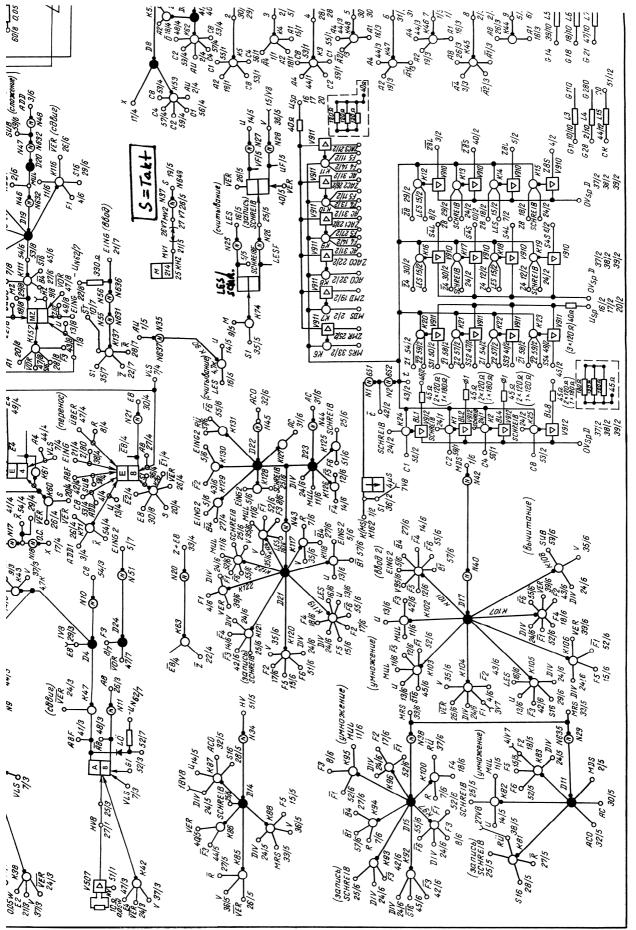

#### II.3.3. Inverter.

The diagram of an inverter shows the logical function « NOT » (negation), the conditions of which a logic 1 signal at output A is only output when input E of the circuit diagram inputs a logic 0 signal, correspondingly, when input E of the circuit is a logic 1 signal, output A of the inverter produces a logic 0 signal.

The circuit of an inverter is executed with a P-N-P type transistor and is a one-stage amplifier.

The logic symbol and schematic circuit diagram of an inverter are given in Fig. 5, on which the dotted line shows the connection point for the source of signals. Let us assume that in the initial state of the inverter diagram a logic 0 signal is applied at input E.

Fig 5. Logic symbol, and circuit diagram of an « Inverter ». Network elements:

| Circuit diagram<br>number | Transistor<br>T1                   | Capacitor<br>C1 | Resistor<br>R1    | Resistor<br>R2 | Resistor<br>R3   |

|---------------------------|------------------------------------|-----------------|-------------------|----------------|------------------|

| Nº 630                    | SA25/2 (2SB75)<br>$\beta = 29-55$  | 1000pF 10% 63V  | 1K5 10%<br>0.125W | 12K 10% 0.05W  | 68K 10%<br>0.05W |

| Nº 631                    | SA25/3 (2SB77)<br>$\beta = 45-88$  | 1000pF 10% 63V  | 1K5 10%<br>0.125W | 12K 10% 0.05W  | 68K 10%<br>0.05W |

| Nº 632                    | SA25/4 (2SB77)<br>$\beta = 72-166$ | 1000pF 10% 63V  | 1K5 10%<br>0.125W | 12K 10% 0.05W  | 68K 10%<br>0.05W |

| Nº 635                    | SA25/4 (2SB77)<br>$\beta = 72-166$ | 1000pF 10% 63V  | -                 | 12K 10% 0.05W  | 68K 10%<br>0.05W |

| Nº 636                    | SA25/3 (2SB77)<br>$\beta = 45-88$  | 2700pF 10% 63V  | -                 | 4K7 10% 0.05W  | 39K 10%<br>0.05W |

| Nº 637                    | SA25/4 (2SB77)<br>$\beta = 72-166$ | 1000pF 10% 63V  | 1K5 10%<br>0.125W | 4K7 10% 0.05W  | 22K 10%<br>0.05W |

| Nº 649                    | SA25/4 (2SB77)<br>$\beta = 72-166$ | 220pF 10% 63V   | 1K5 10%<br>0.125W | 12K 10% 0.05W  | 68K 10%<br>0.05W |

| Nº 651                    | SA25/2 (2SB75)<br>$\beta = 29-55$  | 220pF 10% 63V   | 1K 10% 0.125W     | 12K 10% 0.05W  | 68K 10%<br>0.05W |

| Nº 652                    | SA25/4 (2SB77)<br>$\beta = 72-166$ | 470pF 10% 63V   | 1K5 10%<br>0.125W | 8K2 10% 0.05W  | 47K 10%<br>0.05W |

The source current flows in the chain: +12V, resistors R3, R2, 0V into a logic 0 signal of the applied signals. The current is limited by the resistance of the voltage divider resistors.

A voltage drop across resistor R2 from the current of the input bias source creates on transistor base a positive potential in relation to the emitter, the inverse voltage, applied to the emitter junction, is within the limits of +2V and ensures the non-conducting state of transistor T1. In the base collector chain of the non-conducting transistor flows a current Iko, which creates a small voltage drop across the collector resistor R1. As a result of the non-conducting state of transistor at output A of the inverter a logic 1 is output, until the circuit input E receives a logic 0.

With the connection of a logic 1 signal to input E of the inverter circuit the initial state of C1 shunts the base resistor R2. The negative voltage input logic 1 signal inputs the base and transistor T1 is non-conducting.

In the circuit of the conducting transistor from 0V, T1, R1, -12V flows a collector current, whose value in essence is limited by the resistance of resistor R1.

On the resistance of the conducting transistor thus the current of collector occurs a comparatively small voltage drop. The collector potential becomes close to the emitter potential and so a logic 0 signal is output at point A of the inverter.

Consequently, until input E of the inverter circuit receives a logic 1 signal, output A of the circuit diagram will remain at a logic 0 level.

Capacitor C1 is charged up to the logic 1 signal voltage, the reactance Xc of speed up capacitor C1 increases, to the base current circuit is connected resistor R2, which decreases the value of current, flowing in the chain; 0V, base-emitter of the conducting transistor, resistor R2 in parallel C1, internal is the resistance of the source of signals, -12V. The voltage between the base and the emitter decreases. The base becomes more positive, but preserves negative potential with respect to the emitter. Transistor T1 remains in the conducting state. The value of the base current from the signal source in essence will be determined by the amplitude of the input signal, by the internal resistance of the signal source and by the resistance of the base resistor R2.

The source current of the displacement flows in the chain: +12V, resistor R3, resistance of the base-emitter of conducting transistor, 0v. The resistance of R3 considerably exceeds the value of the resistance of the base-emitter of the conducting transistor. The source current of the displacement, in essence, is determined by the resistance of resistor. R3.

The resistance of resistor R3 is approximately 5-7 times the value of the resistance of the base resistor R2. Consequently, the source current of the displacement will be considerably less than the value of the base current. The counter direction of flow of base and source of displacement creates the resulting current in the section of the chain: 0V, the base-emitter of the conducting transistor. The resulting current creates a voltage drop across resistance the base-emitter of the conducting transistor and ensures the negative potential of the base with respect to the emitter, which retains transistor T1 in the conducting state. The conducting transistor can be characterized by the saturated and unsaturated states and the dependence of the relationship of the currents, flowing in the base and collector chains.

If the input current, multiplied by the mu-factor of transistor, is more than the collector current value of  $\beta Ib \ge \frac{Uk}{Rk}$  that transistor is in the saturated state. If the collector and base current values do not satisfy this relationship, then transistor is in the unsaturated state. The relationship of the current values in the circuit diagram of inverter N630 determines the saturated operating condition of transistor T1. After the end of the logic 1 signal the input of the inverter diagram receives a logic 0 signal.

At the initial moment C1 speed up capacitor shunts the resistor of R2. The base obtains a positive potential with respect to the emitter. Transistor T1 is non-conducting, and output A of the inverter will generate a logic 1 signal. Capacitor C1 is recharged to the value of a voltage drop across resistor R2 from the source current of displacement, the reactance of Xc, increases, to the current circuit of the source of displacement is connected the resistor of R2. A voltage drop across resistor R2 from the current of the source of displacement ensures the non-conducting state of transistor T1.

With the series connection of two inverters the phase of the input signal to input A of the first inverter does not change at output E of the second inverter.

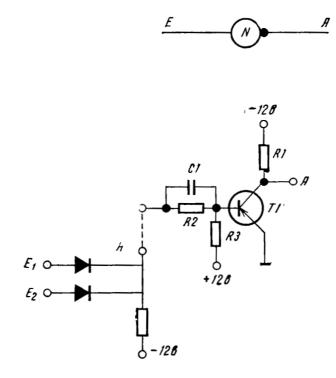

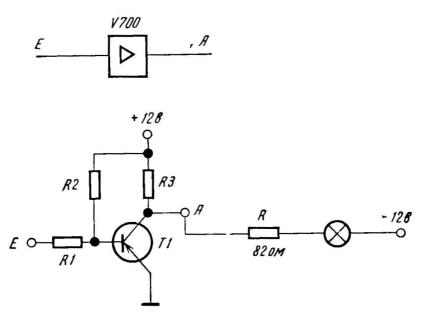

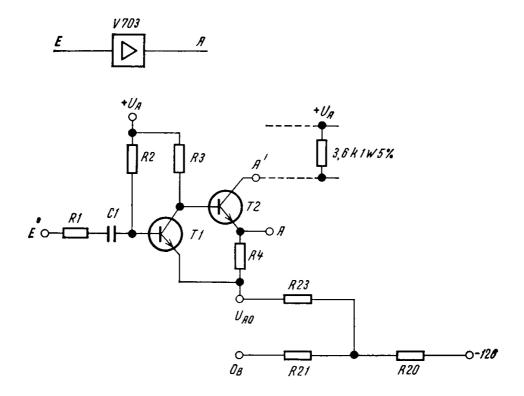

## **11.3.4.** Driver amplifier.

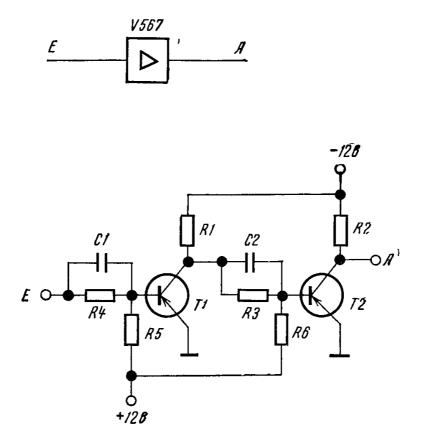

A driver amplifier (V567 circuit diagram) is the two-stage amplifier, assembled from series-connected inverters. In the second inverter a more powerful transistor is used.

Logic symbol and schematic circuit diagram of the amplifier are given in Fig. 6.

In the initial state input E of amplifier circuit receives a logic 0 signal. The current of the source of displacement flows in the chain: +12V, R5, R4, 0V and the source of signals. The voltage divider formed from resistors R5, R4 creates on transistor base a positive potential with respect to the emitter and ensures the non-conducting state of transistor T1. Simultaneously the displacement source current flows in the chain: +12V, resistors R6, R3, R1, -12V. The voltage divider formed from the resistors R1, R3 and R6 creates on the base of transistor T2 a negative potential with respect to the emitter. The forward voltage, applied to the emitter junction, ensures the conducting state of transistor T2.

In the chains: a) 0V, T2, R3, R1, -12V; and b) +12V, R6, T2, 0V in the conducting transistor flow the base currents and source of the displacement, which have a different value and direction. As a result on the base of transistor T2 remains the negative potential with respect to the emitter, which ensures the conducting state of transistor T2. The current value, flowing in the chain 0V, T2, R2, -12V, is limited by the small resistance of the conducting transistor T2 and by resistor R2. In the circuit of the conducting transistor T2 a voltage drop in essence it occurs on the collector resistor R2.

Consequently, until input E of the amplifier receives a logic 0 signal, transistor T2 it is in the conducting state, and output A of the amplifier is at a logic 0 level.

When input E of the amplifier receives a logic 1 signal, at the initial moment capacitor C1's capacity shunts the base resistor R4. The negative voltage of the input signal enters the base of transistor T1.

Fig. 6. Logic symbol and circuit diagram of a « Driver amplifier ». Network elements of V567

| Transistor T1 | SA25/4 (2SB77) | β=72–166 |

|---------------|----------------|----------|

| » T2          | SA25/4 (2SB77) | β=72–166 |

| Capacitor C1  | 1000pF 10% 63V |          |

| » C2          | 2200pF 10% 63V |          |

| Resistor R1   | 820R 0.25W 10% |          |

| » R2          | 330R 0.5W 10%  |          |

| » R3          | 2K2 0.05W 10%  |          |

| » R4          | 12K 0.05W 10%  |          |

| » R5          | 68K 0.05W 10%  |          |

| » R6          | 15K 0.05W 10%  |          |

|               |                |          |

Transistor T1 is conducting and a current is created in the collector circuit: 0V, T1, R1, -12V of the power supply. The value of the collector current is limited by the small resistance of the conducting transistor and by resistor R1. As a result the collector of the conducting transistor T1 generates a logic 0 signal. Capacitor C1 is charged, it's reactance X, increases, to the current circuit of the base is connected resistor R4, which decreases the value of current in the circuit: 0V in, the base-emitter of the conducting transistor T1, R4, and the internal resistance of the source signals -12V.

The voltage between the emitter and the base decreases, so the base becomes more positive, but preserves negative potential with respect to the emitter. Transistor T1 remains in the conducting state.

From the collector of transistor T1 a logic 0 signal enters capacitor C2 and the base resistor R3. At the initial moment the capacitor shunts resistor R3. Positive voltage drop enters the base of transistor T2. The base of transistor obtains a positive potential with respect to the emitter. Transistor T2 is non-conducting.

Capacitor C2 is discharged, the reactance of X, increases, to the chain of the source of displacement is connected resistor R3, which decreases the value of current, flowing in the chain; +12V, R6, R3, T1, 0v, base becomes more negative, but preserves positive potential with respect to the emitter. Consequently, until input E of amplifier receives a logic 1 signal, transistor T2 is in the non-conducting state, at output A of amplifier it is generated the signal E. After the end of the logic 1 signal the input A of amplifier enters a logic 0 signal. Amplifier circuit returns to the initial state. In this case the speed-up capacitors complete the inverter functions. The capacitor C1 decreases the transit time of transistor T1 into the non-conducting state, while the capacitor C2 decreases the transit time of transistor T2 into the conducting state.

As a result the reverse switching of transistors in accordance with the initial state at output A of amplifier circuit a logic 0 signal is generated.

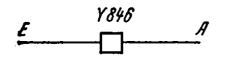

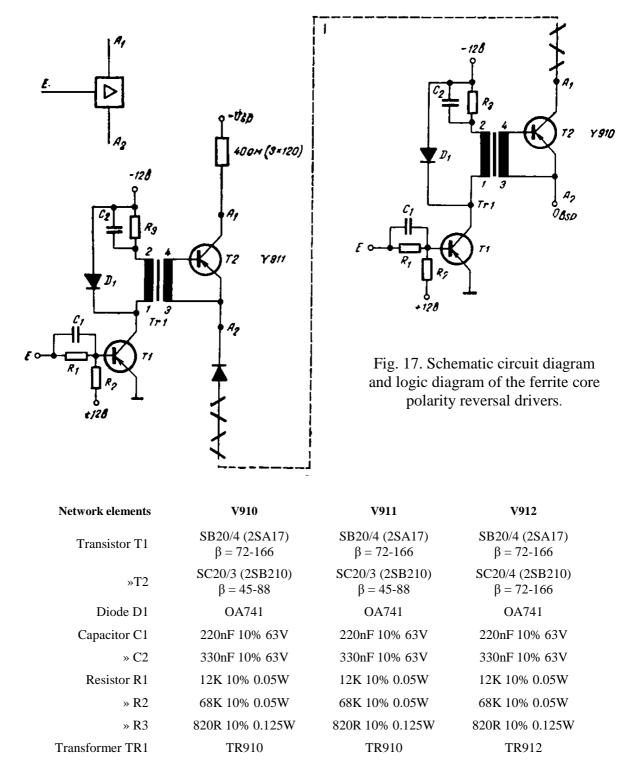

## II.3.5. Read amplifier.

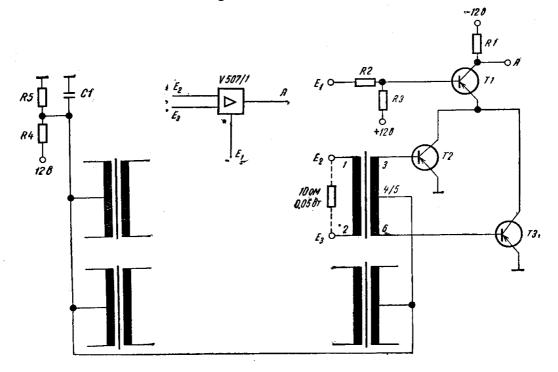

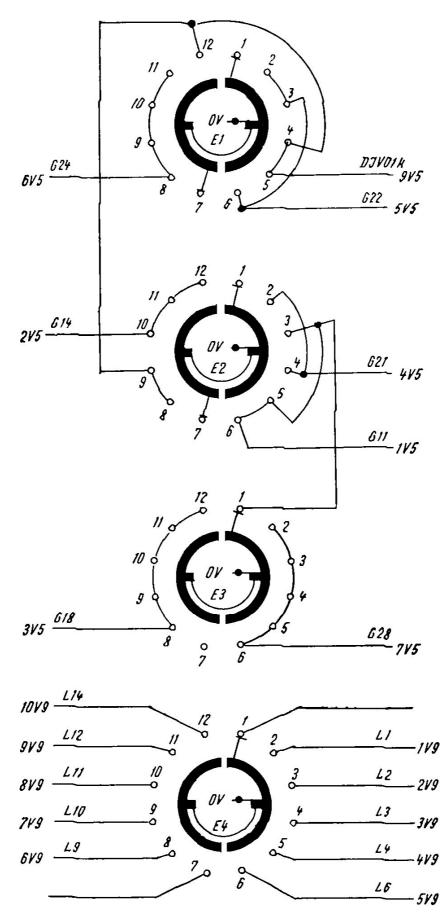

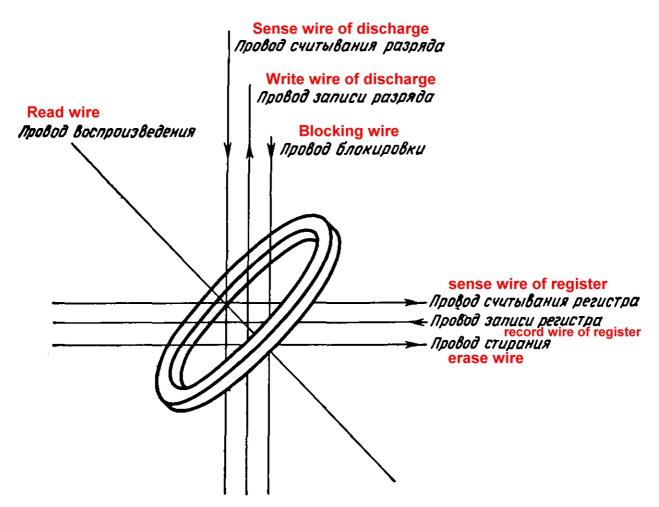

The read amplifiers (diagram V507/1) serve to read the written information from the ferrite cores of the memory block into the four flip-flops of register A.

Readout is produced from pulses induced by a reversal of the magnetization of the ferrite cores, which directs an emf onto the read wire.

In turn the read wire is connected to the inputs E2 and E3 of the read amplifier. Taking into account that the reversal of polarity of ferrite cores occurs also during the record of information, the starting of the read amplifier occurs only when its input E1 receives the special reading signal (HV=1). As a result of the special arrangement and routing of cores in the matrix by the read wire can arise both positive and negative polarity pulses, which in equal measure must act on the amplifier in order to obtain a positive polarity pulse at its output.

A logic symbol and schematic circuit diagram of a read amplifier are given in Fig. 7. In the initial state of amplifier input E1 of the diagram receives a logic 0 signal, the current of the source of displacement flows in the chain: +12V, R3, R2, 0V. A voltage divider formed from resistors R2 and R3 creates a positive potential on the base of transistor T1 with respect to the emitter.

Transistor T1 is in the non-conducting state, at output A of the read amplifier circuit is produced a logic 1 signal.

Simultaneously the current of the source of displacement flows in the chain: +12V, R4, R5, 0V. The voltage divider formed from resistors R4, R5 through the secondary windings of transformers creates on the bases of transistors T2 and T3 of all four amplifiers of reproduction the positive potential, which ensures the non-conducting state of transistors T2 and T3.

Fig. 7. Logic symbol and circuit diagram of a « Read Amplifier ».

Network elements V507/1:

| Transistor T1 | SB20/2 (2SA15)  | β=29–55 |

|---------------|-----------------|---------|

| » T2          | SB20/3 (2SA15)  | β=45-88 |

| » T3          | SB20/3 (2SA15)  | β=45-88 |

| Capacitor C1  | 0.047uF 10% 63V |         |

| Resistor R1   | 10K 0.125W 10%  |         |

| » R2          | 12K 0.125W 10%  |         |

| » R3          | 68K 0.125W 10%  |         |

| » R4          | 6K8 0.125W 5%   |         |

| » R5          | 100R 0.125W 5%  |         |

The operation of the amplifier in shaping the positive polarity pulse at output A of the circuit diagram occurs in the following order. First input E1 receives the drive signal HV=1 and the voltage divider formed from resistors R2 and R3 creates a negative potential on the base with respect to the emitter of transistor T1.

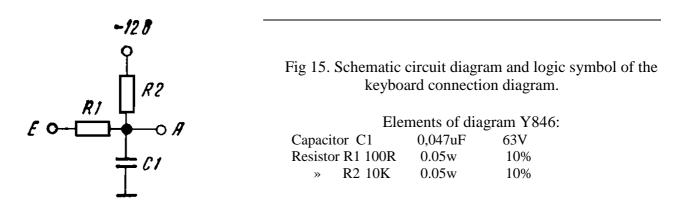

Transistor T1 is conducting and connects the collectors of transistors T2 and T3 to the negative voltage of the power supply -12V.