Wang 600 RAM Testing

Next Log Entry

MOS RAM Basic Tests

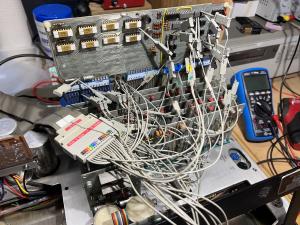

Testing so far has demonstrated that after PRIME is released the ROM address lines show a sequence of addresses that are similar to those seen in an emulated Wang 600. This suggests that the ’next instruction’ bits of the ROM and their associated logic circuits are significantly functional. Microcode appears to be running but the machine shows no function so there must be errors in other bits in the ROM, or the microcode engine, or perhaps in the RAM.

The 6183 RAM board uses early Mostek 4008P 1K x 1 bit MOS dynamic RAMs. DoPECCs Wang 600 has two of a possible 4 banks of chips populated, for a total of 2K 4-bit words.

RAM Power Saving

Surprisingly, the schematics include transistor switches on the -12v supply to each 1k x 4 RAM bank and these turn out to be implementing a power saving mode for the RAM chips. If the -12v supply is allowed to go to ground, data is still retained but power dissipation is reduced. The -12v must be restored before any RAM read or write can occur and must also be restored for RAM refresh cycles which are required at least every 2mS. The result is a piece of moderately complex logic and switching in order to reduce a fully populated 4k machine’s RAM power consumption from 2.4W to 800mW. It’s difficult to understand the motivation for this design in a machine that was mains powered but perhaps the overheating problems that plagued the earlier Wang 700 series machines were still very much in mind when the 600 machines were in design.

It seemed important to check that this basic function was operating, without correct power no RAM can function.Setting up the storage scope on the RAM power lines demonstrated that the -12 was switching in a manner that seemed reasonable.

RAM Address and Data Testing

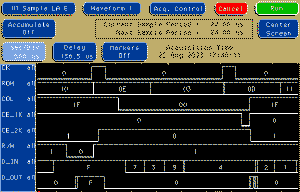

The RAM address, chip select and data in/out lines were then instrumented with the HP16500C Logic Analyzer and it could be seen that the RAM Row Address lines were counted backwards from 0x1F to 0x00 at the start of each machine cycle and that other addresses appeared later in the cycle. This could be consistent with RAM refresh, followed by whatever actual RAM data operations may be required.

The RAM Column Address lines alternated between 0x00 and 0x1F. This was accepted as showing some kind of dynamic activity.

Scrolling through the tracings showed a scattering of RAM address and data in/out activity, suggesting that the RAM was producing data of some sort.

Later discoveries were to show that more attention should have been given to the Column Address Lines that only showed ‘all on’ or ‘all off’

Previous Log Entry Back to Log Index Next Log Entry